# Electrical-Level Attacks on CPUs, FPGAs, and GPUs: Survey and Implications in the Heterogeneous Era

DINA G. MAHMOUD, EPFL, Switzerland VINCENT LENDERS, armasuisse, Switzerland MIRJANA STOJILOVIĆ, EPFL, Switzerland

Given the need for efficient high-performance computing, computer architectures combining CPUs, GPUs, and FPGAs are nowadays prevalent. However, each of these components suffers from electrical-level security risks. Moving to heterogeneous systems, with the potential of multitenancy, it is essential to understand and investigate how the security vulnerabilities of individual components may affect the system as a whole. In this work, we provide a survey on the electrical-level attacks on CPUs, FPGAs, and GPUs. Additionally, we discuss whether these attacks can extend to heterogeneous systems and highlight open research directions for ensuring the security of heterogeneous computing systems in the future.

CCS Concepts: • General and reference  $\rightarrow$  Surveys and overviews; • Hardware  $\rightarrow$  Reconfigurable logic and FPGAs; • Computer systems organization  $\rightarrow$  Embedded and cyber-physical systems; System on a chip; Heterogeneous (hybrid) systems; Reconfigurable computing; • Security and privacy  $\rightarrow$  Side-channel analysis and countermeasures; Hardware attacks and countermeasures; Hardware reverse engineering.

Additional Key Words and Phrases: electrical-level attacks, heterogeneous computing systems, CPU, FPGA, GPU

#### **ACM Reference Format:**

Dina G. Mahmoud, Vincent Lenders, and Mirjana Stojilović. 2022. Electrical-Level Attacks on CPUs, FPGAs, and GPUs: Survey and Implications in the Heterogeneous Era. ACM Comput. Surv. 55, 3, Article 58 (February 2022), 37 pages. https://doi.org/10.1145/3498337

# 1 INTRODUCTION

A recent trend in high-performance computing is to combine various computing units to achieve better performance; these include central processing units (CPUs), graphics processing units (GPUs), and field-programmable gate arrays (FPGAs). Each of these computing units is better suited for some workloads than others, thus allowing the versatile high-performance computing workloads to exploit the full potential of a *heterogeneous computing system* (HCS).

In the most generic terms, a heterogeneous system includes a variety of computing platforms with numerous interconnect methods and integration levels between the components. With their chip-level integration, embedded *system-on-chip* (SoC) and multiprocessor system-on-chip (MPSoC) platforms are among the most notable examples of HCSs. Besides them, today's cloud computing architectures are another notable representative of heterogeneous architectures, as they provide the users with a combination of CPUs, GPUs, and FPGAs.

Authors' addresses: Dina G. Mahmoud, dina.mahmoud@epfl.ch, EPFL, Lausanne, Switzerland; Vincent Lenders, vincent.lenders@armasuisse.ch, armasuisse, Bern, Switzerland; Mirjana Stojilović, mirjana.stojilovic@epfl.ch, EPFL, Lausanne, Switzerland.

This research is supported by armasuisse Science and Technology. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2022 Association for Computing Machinery. Manuscript submitted to ACM

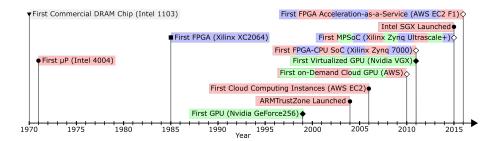

Fig. 1. Timeline of the evolution of computing systems, highlighting the introduction of various compute units, their integration, and their availability to cloud users. CPU milestones are highlighted in red (full circles), GPU milestones are highlighted in green (full rhombi), and FPGA milestones are highlighted in violet (full squares). Heterogeneous milestones are distinguished by the multiple colors (hollow rhombi), while the DRAM milestone is highlighted in grey (full triangle).

While the concept of heterogeneous computing has been studied for more than two decades [52], with the recent advances in FPGAs and GPUs, the HCS systems themselves have greatly evolved. HCSs have become a platform of choice for a multitude of highly parallel tasks, commonly not executed efficiently by CPUs, e.g., image processing and machine learning (ML) algorithms. The large-scale adoption of heterogeneous systems has, in turn, led to the development of programming standards for hybrid architecture platforms (e.g., OpenCL [201]) and standardization of the architectures (e.g., heterogeneous system architecture (HSA) [90]). Furthermore, as shown in Figure 1, a number of commercial heterogeneous platforms have recently become available, both in the cloud and in embedded form.

However, the security of HCSs is still neither fully investigated nor understood. Not surprisingly, researchers in system security have mostly been focusing on attacks on CPUs; vulnerabilities in the CPU software have long been analyzed, starting with the Morris worm in 1988 [51]. Code injection and return-oriented programming are other well-known classes of software attacks [184, 221]. More recently, attacks taking advantage of the processor microarchitecture (e.g., Spectre [104] and Meltdown [119]) have drawn considerable attention, together with the famous disturbance error-based attack on dynamic random access memories (DRAMs), known as RowHammer [102]. The observable side effects of code execution on CPUs—at the electrical level, there are power consumption and electromagnetic (EM) emanations and, at other levels, sound waves—have been used for side-channel analysis (SCA) attacks [188]. CPUs are also subject to fault-injection attacks, either via physical access to the device or, as recently shown, remotely [13, 99, 157, 173, 174]; fault injection can rely on the EM field, voltage, or frequency, but it can also be optical- or temperature-based [13].

We can observe a similar trend for FPGAs, which have only recently been integrated into a number of cloud infrastructures [6, 7, 91]. FPGAs are known to be vulnerable to fault injection and side-channel attacks when the attacker has physical access to the device [88, 241]. Not long ago, researchers have shown that these attacks on FPGAs can even be controlled and executed remotely [73, 236]. And finally, GPUs, being similar to CPUs in many respects, share a number of their vulnerabilities; microarchitecture-based side channels [96] and power side-channel analysis [124] have been demonstrated on GPUs. Furthermore, FPGAs and GPUs can help accelerate some of the attacks on CPUs, notably microarchitectural and RowHammer exploits [58, 224].

When CPUs, FPGAs, and GPUs are brought together in a heterogeneous system, the resulting system-level security vulnerabilities are no longer limited to the existing and known exploits of each individual component: New exploits may arise due to the component integration. While not as extensively researched as the attacks focusing on individual computing units, security of HCSs has been looked into: Researchers have demonstrated covert channels, side channels, and RowHammer attacks across the system components [58, 68, 77, 224]. However, more research is necessary to Manuscript submitted to ACM

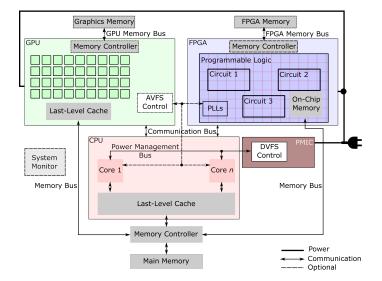

Fig. 2. A representative example of a heterogeneous system architecture. Optional parts are shown with dashed lines. The connections between components serve for communication or power delivery (thick lines).

identify, understand, and overcome the security risks brought up or aggravated by the close integration of diverse processing units.

In this paper, we present a survey of the attacks on CPUs, GPUs, and FPGAs. In particular, we focus on electrical-level attacks because, unlike microarchitectural or software-based attacks, their underlying mechanism is typically not platform-dependent; hence, they have the potential to affect all considered processing units. We examine RowHammer, fault injection, and SCA attacks. Unlike other surveys, which focus on only one compute unit, one exploit type, or one threat model [15, 158, 179, 188, 211, 232, 233, 237], we include in our examination all three computing units and take into consideration the heterogeneous system architecture and deployment models.

The rest of this paper is organized as follows. We start by presenting the heterogeneous system architectures and the associated threat models in Section 2. We then provide a classification of the attacks in Section 3. We survey and discuss the known attacks on CPUs, FPGAs, and GPUs in Sections 4, 5, and 6, respectively. In Section 7, we discuss whether the electrical-level attacks described previously can affect heterogeneous systems and which new attacks may be feasible in a heterogeneous setting. Section 8 concludes the paper.

## 2 HETEROGENEOUS SYSTEMS AND THREAT MODELS

We begin a thorough analysis of the electrical-level vulnerabilities of heterogeneous systems by examining their common architectures and variations thereof. Widely-deployed embedded heterogeneous platforms include the SoCs by Xilinx and Intel, which tightly integrate CPUs with FPGAs [8]. Xilinx even offers an MPSoC option with GPUs [242]. In the cloud market, both Intel and Xilinx have their share, with the accelerator cards deployed in AWS [7], Microsoft [142], Alibaba [6], and Huawei [91] cloud instances. Of course, GPUs are available as well. In this section, we distinguish heterogeneous systems by their integration style: *chip level* and *system level*. We show a generic heterogeneous architecture in Figure 2 and highlight the differences between the two integration styles in the following subsections. We end this section with the explanation of the threat models.

#### 2.1 Chip-Level Heterogeneity

Chip-level heterogeneity is heterogeneous integration inside the device package. As a generic example, we choose here the Zynq UltraScale+ MPSoC from Xilinx [242], which combines an ARM processor with a GPU and an FPGA. It has an application processing unit—the CPU of the system—and a real-time processing unit. The components communicate via the advanced extensible interface (AXI) [242] (communication buses in Figure 2), common in Intel SoC platforms as well (e.g., Cyclone V [45] and Arria 10 [8]).

Access to the main memory is often shared among components; on heterogeneous CPU-GPU platforms, both components can access the main memory, and the GPU can use both coherent and noncoherent communication [32]. In the Xilinx UltraScale+ MPSoC device, all three components can access the external DRAM through the memory controller, which exposes the system to the risk of RowHammer exploits. Additionally, the memory can be partitioned to provide isolation between multiple users or applications [140], which may provide some protection. Memory-to-memory and memory-to-IO transfers take advantage of the direct memory access (DMA)—common in Intel Cyclone V and Arria 10 SoCs as well [8, 45]—with the number and rate of access requests handled by the transaction control mechanism [242].

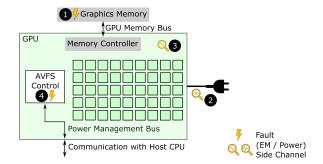

The ARM processor supports the trusted execution environment (TEE) called TrustZone, a target of recent attacks, and frequency scaling, a facilitator of recent attacks [8, 45, 242]. Software interfaces allow the CPU cores to communicate the desired frequency to the dynamic voltage and frequency scaling (DVFS) control, via the power management bus (PMBus). Sometimes, GPUs allow frequency scaling (controlled from the CPU side [63], and known as adaptive voltage and frequency scaling (AVFS)), but that is not the case in the UltraScale+ MPSoC. For FPGAs in general, the clock management resources—phase-locked loops (PLLs) and mixed-mode clock manager modules—can be configured by the FPGA applications or by the CPU. While FPGA voltage scaling is typically not supported, if the on-board voltage regulators support it, the PMBus may be used to control the voltage supplied to the FPGA [186]. Since the programmable logic (PL) shares the power distribution network (PDN) (the FPGA grid in Figure 2), the result is free propagation of voltage disturbances across the die and, consequently, a number of electrical-level attacks on FPGAs (Section 5).

In the SoCs with an ARM processor (e.g., Intel Cyclone V), it is possible to poll the CPU power and temperature from software [45]. On the other side, Xilinx UltraScale+ MPSoC is equipped with a system monitor, which reports the voltage and temperature at various on-chip locations (in the processing system and the PL). This MPSoC is divided into power-gated islands for turning off unused parts of the system—a feature not unique to Xilinx SoCs [45]. The existence of power-gated islands could suggest that different system components require different voltage levels; in reality, this is often not the case. As a consequence, the PDN design is simplified (the number of voltage regulators reduced), but the risk of electrical-level attacks is increased (as discussed in Section 7).

## 2.2 System-Level Heterogeneity

Datacenters (and cloud) are a typical example of system-level heterogeneity. In datacenters, GPUs and FPGAs lie on their respective accelerator cards, plugged into the server racks and connected with the CPUs through peripheral component interconnect express (PCIe), quick path interconnect (QPI), or ultrapath interconnect (UPI) (the last two being common to Intel Xeon+FPGA platforms, available to researchers through the Intel Hardware Accelerator Research Program (HARP) [38]). Even though the coupling through the common power supply is lower than for chip-level integration, it is not fully eliminated, because all the cards in one rack share a common power supply unit.

Besides having access to the CPU's main memory, FPGAs and GPUs can also have their own memory modules (Figure 2). In that case, for performance reasons, data is typically moved in bulk between the CPU main memory and the accelerator memory [38]. The specifics of voltage and frequency scaling largely depend on the CPU and GPU used. As far as FPGAs are concerned, the clock management resources can be configured by the users. Access to voltage and frequency interfaces can sometimes be hindered by virtualization: CPUs are typically virtualized, while GPUs can be virtualized, e.g., using rCUDA [48] or Nvidia virtual GPU [217]. While many virtualization proposals exist for FPGAs [176], the hardware of cloud FPGAs is currently not abstracted away. Finally, despite the number of research works on voltage and frequency scaling on FPGAs [4], these techniques are not yet supported in heterogeneous settings.

#### 2.3 Threat Models

Regardless of the integration level, various assumptions can be made on how an adversary may have access to the platform and what the adversary can do, depending on the deployment scenario. From appliances to internet-of-things (IoT) devices, embedded systems are everywhere. Many of the embedded devices (e.g., IoT sensor nodes) are connected to the network, for sending their data to the users or providing access to the device itself. In this case, the heterogeneity is typically at the chip level. Even though multitenancy is typically not considered in embedded scenarios, hardware Trojan horses from third-party intellectual property or malicious chip manufacturers, as well as malicious software, can create covert communication channels or interfere with the operation of the device. Both an attacker with direct access to the hardware (with the possibility of removing the integrated circuit (IC) package, or probing and measuring the external signals) as well as an attacker with remote access are valid threat model assumptions. Furthermore, both chip-level and system-level heterogeneous devices may be the attack targets.

In the cloud deployment scenario, a malicious user with remote access may be assumed to either have user privileges or to have gained (legally or not) root privileges. For FPGAs, a typical assumption is that each device has a soft programmable shell that manages the use of FPGA resources. At the same time, the FPGA users can share the logic and hardened resources temporally or spatially. In the case of spatial cotenancy, the roles are assumed to be logically separated, while the PDN remains common. It is interesting to note that, even though there are a number of proposed solutions for FPGA virtualization [214] (driven by the benefits of multitenancy and low implementation effort, thanks to the partial reconfiguration feature of FPGAs), due to the recently discovered electrical-level security risks that FPGA multitenancy creates, no cloud service provider (CSP) allows it yet.

If an adversary has physical access to the datacenter rack or root privileges, then some threat models assume the availability of TEEs—e.g., ARM TrustZone or Intel software guard extensions (SGX)—for isolating the execution of users' code. However, TEEs do not provide full protection against all adversaries with physical access [37]. In case of FPGAs, physical access means control over the shell and, consequently, over the clock or data.

# 3 BACKGROUND AND TAXONOMY

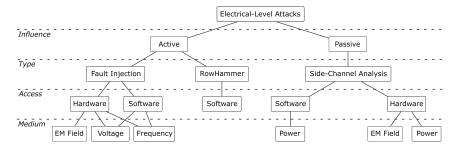

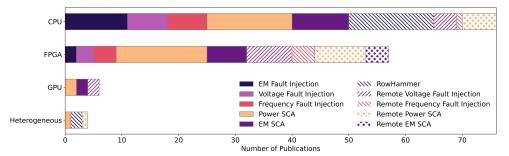

Electrical-level attacks are common to all system constituents, albeit the exact interface exploited to carry them out may differ depending on the target. These attacks can have an *active* or a *passive* influence on the target. A passive attack simply observes the target, without affecting it. An active exploit, however, requires interfering with the target's functionality. Figure 3 illustrates the taxonomy of electrical-level attacks common to CPUs, FPGAs, and GPUs. Figure 4 highlights the current state of research (approximated by the number of publications addressing new or enhanced attacks that we cite in this paper) and, in a way, applicability of a particular type of attack to either a specific processing

Fig. 3. Classification of the electrical-level attacks common to CPUs, FPGAs, and GPUs.

Fig. 4. Current state of research on the electrical-level attacks targeting individual processing units or heterogeneous systems.

unit or a heterogeneous system. The figure shows that CPUs and FPGAs have so far been the most attractive attack targets. In the following subsections, we introduce the three main attack types and further explain the taxonomy.

# 3.1 RowHammer

We consider *RowHammer* as a distinct type of active software-based electrical-level attacks. The goal of RowHammer attacks is to induce errors in DRAM memory, with consequences affecting the entire system.

DRAM process technology is continuously scaled to pack a larger number of smaller cells in one module. However, this comes at a cost of reduced memory reliability, as the smaller cell size and the tighter spacing between the cells favor EM coupling effects, which can affect the leakage rate of the charge stored in each cell, representing one bit. Other scaling effects include the reduced noise margins and higher variation in process technology [102].

If a cell leaks more charge than its noise margin, a fault occurs [102]. To avoid the leakage, DRAM rows of cells are regularly refreshed. Nonetheless, attackers can leverage a phenomenon known as *disturbance* to exploit the leakage in DRAM cells and induce faults. This phenomenon occurs when neighboring cells interfere with each other's operation; when a cell is disturbed beyond its noise margin, it malfunctions, resulting in a *disturbance error*. In 2014, Kim et al. showed that repeatedly accessing a row in the DRAM can interfere with neighboring cells, resulting in disturbance errors [102]. DRAM manufacturers employ circuit-level design techniques (to improve the isolation between cells) and post-production testing to ensure that chips arriving to the users do not suffer from disturbance errors. However, with the continued scaling of DRAM cells, these mitigations are no longer sufficient; Kim et al. highlight this insufficiency by showing that DRAM modules manufactured after a specific date are prone to the RowHammer-induced faults [102].

Inducing bit flips in the target DRAM requires the adversary to be able to access it. This access is possible when the adversary resides on the same system or can use DMA over the network (e.g., Throwhammer [207]). The feasibility of Manuscript submitted to ACM

inducing RowHammer bitflips mainly depends on the target DRAM, but researchers keep demonstrating the feasibility even on DRAM modules previously assumed to be immune [59]. As will be discussed later, a successful attack also requires the bitflips to be induced in an exploitable location, which can be ensured through some knowledge of the target, physical addresses, or the electrical or microarchitectural side channels. Bitflips in other locations may either crash the system or not prove useful to the attacker. Since the adversary does not need to access the victim row, access to the part of the memory belonging to the victim is not required. However, in some cases, memory deduplication is useful for enabling the attack by sharing pages between the victim and the adversary [180]. The RowHammer attack vector is particularly dangerous because it is entirely software-controlled, not requiring access to the hardware; moreover, RowHammer has been used in realistic scenarios, where the CPU was the intended victim. Most of the exploits were initiated from (and targeting) the CPU, but a few were launched from an FPGA, a GPU, or the network [58, 207, 224].

## 3.2 Side-Channel Analysis

For decades, it has been known that computing systems leak information through side channels (e.g., power consumption or electromagnetic emanations) [208]. This leakage has been exploited as an attack vector for reverse engineering [39, 175] and for breaking the security of cryptographic primitives [105].

Electrical side channels are created by the existence of mutual information between the code being executed and the data being processed, on the one side, and the resulting power consumption and EM emanations, on the other side. The most common techniques for extracting the information are simple power analysis [179], differential power analysis (DPA) [105], correlation power analysis (CPA) [29], template attacks [36], mutual information analysis [70], and machine learning [84]. Machine learning approaches are particularly adapted for side-channel disassembly (reverse-engineering of the executed code, mainly on a CPU), as the dimensionality of the problem and the size of the data to be recovered is much higher than in the case of side-channel cryptanalysis [166].

SCA can be seen as a passive attack as the main requirement is the observation of the side effects of the code execution. The side-channel information may be obtained through hardware access or through a software interface (recent research trend for FPGAs). When an adversary has access to the hardware, the SCA may be *invasive*, if, for instance, the IC package needs to be removed or manipulated; most commonly, it is *noninvasive*. In a laboratory, researchers may opt for the invasive model, adding resistors for measuring the power consumption, or decapsulating the IC for observing EM emanations. In realistic settings, depending on where the victim is deployed and how it is protected, a noninvasive attack may be more appropriate (leaving no trace of the attack). If the adversary resides on the same system as the victim then software-based exploits are feasible through power monitoring interfaces, or the ability to reconfigure FPGA logic to act as a sensor. If the victim provides a public interface through which the adversary may send input data, then the attacker can fix the input to a predefined value and collect leakage traces to learn the secret (i.e., known plaintext attack). EM-based side channel exploits (except for crosstalk coupling on FPGAs) require hardware access to the victim. However, unlike hardware power-based SCA, EM-based SCA does not require adding a resistor for measurements or connecting a voltage probe to one of the IC's pins, but rather only an EM probe positioned near the IC.

# 3.3 Fault Injection

The clock frequency and power supply voltage govern the correct operation of digital circuits, including the ones inside a processor. For a specific frequency value, there exists a minimum voltage value, known as the critical supply voltage, to ensure correct operation of the circuits. If these values are not respected, the circuit experiences errors.

Fig. 5. Illustrative system architecture for a CPU-only system, with interfaces vulnerable to fault and side-channel attacks highlighted. The circled numbers indicate the vulnerabilities we discuss. The symbols indicate the attack type.

In 1997, Boneh et al. introduced the threat of fault injection to cryptographic circuits, highlighting how to use hardware faults, leading to random transient bit flips, to break Rivest–Shamir–Adleman (RSA) and Rabin signatures [23]. Such transient faults can be injected in many ways; if the clock frequency is too high or the clock signal contains glitches, inputs to registers in the circuit may not arrive early enough to be processed by the register, resulting in early latching or metastability. Even if the clock frequency is within limits, lowering the supply voltage results in longer signal delays, which again can lead to computational faults. The number and distribution of faults depends on whether the voltage has fast (glitches) or steady changes [97]. Low-power applications pushed for the emergence of dynamic voltage and frequency scaling (DVFS) techniques, which, as it turns out, can be abused for remote fault-injection attacks against CPUs and GPUs [173, 185, 206].

Fault-injection exploits are active attacks, because they require interfering with the target operation. They can be carried out via software access only (e.g., by controlling the DVFS interfaces of the CPU or by programming the FPGA). If available, hardware access may give the adversary direct control over the power supply or the clock, thus simplifying the fault injection. In a lab setting, to facilitate the attack, the on-board capacitance could be manipulated or the chip connected to the attacker-controlled power supply [209]. Even though such changes may not be possible in all realistic scenarios, they allow researchers to assess the susceptibility of the victim to the exploit. Attack success can sometimes be facilitated by prior observations of side-channel leakage to determine when precisely to inject the faults. Exploiting the injected faults typically requires the attacker to be able to observe the output (e.g., for differential fault analysis) or run a software process on the victim device to gain special privileges thanks to the injected faults.

# 4 ELECTRICAL-LEVEL ATTACKS ON CPU-BASED SYSTEMS

Let us begin the survey of attacks (and the corresponding defenses) focusing on the CPU-based systems. Figure 5 shows their simplified architecture and highlights both the components and interfaces vulnerable to fault and side-channel attacks. In the following subsections, we discuss them all, following the taxonomy introduced in the previous section.

# 4.1 RowHammer Attacks

Kim et al. were the first to exploit the DRAM memory sensitivity to disturbance faults for creating bit flips [102]. In what they named a RowHammer attack, ① in Figure 5, disturbance errors were induced by repetitive opening of a DRAM row, access (read or write), and closing.

Depending on the location of the bit flip, various effects can occur; for example, bypassing the authentication carried out by cryptographic codes, application crashing, persistent loss of data, or file system damage [207]. Modern DRAMs, Manuscript submitted to ACM

with their increased density and without mitigations, are more vulnerable than older DRAMs to RowHammer [101]. On recent DDR4 modules, which were previously considered immune to RowHammer, Frigo et al. demonstrated many-sided RowHammer attack (with as many as 19 aggressor rows); they uncovered how to bypass the target row refresh countermeasure, deployed in DDR4 [59].

RowHammer attacks can be combined with cache or memory deduplication side channels to cause more harm to the system. Seaborn and Dullien were the first to achieve privilege escalation from a process running locally on the victim machine, by flipping bits in the physical page number of page table entries [192]. Privilege escalation from an unprivileged Android app was also demonstrated on ARM mobile devices by van der Veen et al., who relied on the predictability of memory allocation patterns to ensure the victim will allocate its page table entries in RowHammer-vulnerable memory locations [215]. TEEs are also affected by RowHammer bit flips, which can be leveraged by a remote attacker with no system privileges for denial-of-service (DoS) attacks on SGX enclaves [94].

While the requirement for the main memory access suggests the need for a flush instruction (to bypass the cache), recent works have demonstrated successful RowHammer exploits without it: Qiao and Seaborn used x86 nontemporal instructions to bypass the cache [171], Aweke et al. used eviction sets [10], useful for remote exploits by unprivileged adversaries as well [80], while Van der Veen et al. used DMA on ARM mobile devices [216].

Coupling the RowHammer attack with a website with JavaScript makes for a remotely-controlled attack, allowing the adversary to gain memory access, or break the memory isolation and access another virtual machine on the same CPU [25, 80, 180]. An adversary can also use network packets to induce bit flips in the memory [120], and remote DMA can allow a foe to gain code execution rights on a key-value server application [207]. Most recently, Cojocar et al. formalized the method for determining whether a cloud server is vulnerable to the RowHammer attack and designed a fault injector that enables reverse engineering the row adjacency map of DDR4 modules [41].

4.1.1 Countermeasures. Given that decreasing the refresh interval of DRAM modules can impede and, at a certain point, stop RowHammer attacks, the first proposed countermeasure was to increase the refresh rate; this was implemented by some of the memory manufacturers, e.g., Apple and HP [158]. However, the refresh rate increase comes at the cost of higher energy consumption, lower system performance, and a degradation in the quality of service. Kim et al. found that a refresh rate increase by a factor of at least 7.8× was needed to eliminate all RowHammer-induced errors [102]. Other countermeasures can be classified as software- or hardware-based.

ANVIL is an example of a software-based countermeasure, which makes use of the hardware performance counters to find if a memory access pattern indicative of a RowHammer attack is occurring and, if needed, refreshes the affected DRAM cells [10]. Alternatively, one can modify the page allocation to ensure that an attacker cannot impact important memory pages [28]. GuardIon takes a similar approach, isolating the DMA buffers on ARM devices to prevent DMA-based RowHammer [216], and so does ZebRAM: It isolates every row containing data with guard rows, which can be filled with other data and protected using integrity checks [106]. Vig et al. proposed using dynamic skewed hash tree to quickly detect RowHammer exploits [218]. It has been found that static code analysis can help identify malicious software (e.g., MASCAT [93]). However, all software-based solutions are costly, as they require modifications to the system software, incur performance or memory overheads, or interfere with the system operation [158].

Turning to the hardware-based solutions, some of them are quick to implement; for example, remapping or retiring vulnerable cells in the DRAM. While not requiring significant hardware changes, discarding the unsafe cells requires first their dynamic identification, resulting in time, effort, and storage overhead [102]. Other short-term options make use of the error correcting code modules, if available. However, error correcting codes incur considerable overhead

and often correct only single-bit errors, while RowHammer can induce multiple bit flips [102]. On the other hand, some hardware solutions focus on the long term protection: Modifications to the memory controller or to the memory module—such as the probabilistic adjacent row activation (PARA) mechanism proposed by Kim et al. [102] and the probabilistically managed table by Son et al. [198]—provide good security guarantees. Some versions of the probabilistic defenses are already deployed in recent Intel memory controllers [158]. Other possibilities include adding hardware counters (e.g., counter-based tree [196] and time window counters [116]) in the memory controller. More recently, Yağlıkčı et al. proposed BlockHammer, which throttles the rate at which a single DRAM row can be accessed to avoid bit flips [227]. BlockHammer also limits the memory requests by suspicious threads, ensuring that benign threads can still benefit from a good memory bandwidth. EM side channels, which we discuss in the following subsection, have also been proposed as detection methods for RowHammer attacks [235]. While many countermeasures are discussed, the deployment of effective defenses is still underway, and new research demonstrates persisting vulnerabilities.

## 4.2 Side-Channel Attacks

CPUs have long been a target of side-channel attacks [105], with the goal of breaking the security of cryptographic algorithms or, more recently, reverse-engineering the code running on the CPU (i.e., side-channel disassembly). SCA attacks typically require hardware access to the device, but recent works have shown the feasibility of software-based exploits via the power management interfaces [118]. Here, we discuss both hardware- and software-based exploits.

4.2.1 Hardware Side-Channel Attacks. An adversary with physical access to the device can gain information about the code executing on that device, often sufficient for compromising secure data and proprietary code. In what follows, we examine the use of that information for side-channel cryptanalysis and disassembly. While we focus on the malicious exploitability of side-channel disassembly, it is worth noting that it can also be used for system protection [83, 165].

Power. From the first efforts to develop a power-based SCA [105], ② in Figure 5, the hardware security research community has shown significant interest in these exploits. Since the works showing the dangers of variable latency of cryptographic operations [79], algorithms have improved to overcome obvious vulnerabilities; yet, researchers are continuously bringing to light new exploits [179, 237]. Genkin et al. underscored the extent of the threat of power SCA by extracting 4096-bit RSA keys and 3072-bit ElGamal keys from personal laptops, using power and EM measurements at the chassis and at the end of a USB or an HDMI cable [65]. Surely, design choices play an important role in side-channel resistance: Biryukov et al. analyzed the factors that render a cryptographic implementation more secure against a CPA attack and validated their findings on eight different lightweight ciphers and an 8-bit ATmega2561 processor [22].

A successful side-channel attack typically requires multiple measurements (i.e., traces) [40]. To overcome this limitation, Clavier et al. proposed horizontal correlation analysis, which, with one known message to encrypt, exploits the similarity of operations and data within one algorithm execution [40]. They used a single power trace from an exponentiation process of the RSA algorithm on a RISC processor. Even though their method does not work against all implementations (e.g., RSA with Chinese remainder theorem), it demonstrates that there are approaches that help optimize the exploit. Batina et al. used a single trace to learn the input to a publicly available multi-layer perceptron (MLP), relying on the sequential computations in an ARM Cortex-M3 [18]; given that in the first layer of a neural network (NN) multiple weights (known in this scenario) are all multiplied by the same input (the secret), the side-channel traces during multiplication enable the recovery of the secret. While ML models can be targets of exploits, they can also help facilitate the attacks [85, 89] or decrease the number of required traces [223]. Masure et al. proved that the optimization which takes place during ML training is equivalent to maximizing the obtained side-channel information [136].

Parallel to works using side-channel leakage to reveal secret information processed by a CPU, researchers began to investigate if this leakage could disclose more secrets, notably the executed instructions. Quisquater and Samyde were the first to demonstrate automated instruction reverse-engineering, on a Zilog Z80 processor, using power and EM traces [175]; their use of a Kohonen NN was indicative of the observed trend of employing ML in subsequent research on side-channel disassembly. Eisenbarth et al. instead relied on hidden Markov models to build a power side-channel disassembler targeting a PIC microcontroller and resulting in a recognition rate of up to 70% [50].

Recent works continue the trend of ML-assisted disassembly [113, 166, 212]. Park et al. focused on attacks on IoT devices, conducting experiments on the AVR ATmega328p processor and analyzing 112 instructions and 64 source and destination registers [166]. Taking advantage of continuous wavelet transform to observe differences between instructions not observable in the time domain, Park et al. then applied a feature selection method to reduce the required number of samples. They examined a number of classifiers: linear discriminant analysis, quadratic discriminant analysis, naïve Bayes and least squares support vector machine (LS-SVM), and developed a full disassembler for monitoring the code execution on embedded processors, with security as the main aim. They used hierarchical classification, thus reducing the computational complexity, and a covariate shift adaptation to overcome the effects of changes in the measurement environment. With quadratic discriminant analysis, the classification accuracy reached 99.03% [166].

When the number of clock cycles per instruction (CCPI) varies, disassembly becomes more complicated; Krishnankutty et al. found the optimal sequence of clock-cycle lengths on a general-purpose pipelined processor (MSP430G2553), using empirically created templates together with dynamic programming [113]. Once the CCPI is known, the next step is to find the correct instruction among those with the given CCPI. Between the two steps, one can resort to a coarse-grained classification according to the hardware usage, which Krishnankutty et al. implemented using a SVM (92–100% accuracy). In comparison, the fine-grained classifier tested on real instruction sequences (advanced encryption standard (AES) and proportional-integral-derivative controller) resulted in about 86% accuracy. Similarly, Vafa et al. used a hierarchical framework for instruction recognition on an 8-bit PIC and a 32-bit ARM Cortex-M3 microcontroller, with both static and dynamic power measurements, achieving 80–93% recognition rate [212].

EM Field. Power traces are not the only side channel, as EM emanations, ③ in Figure 5, can provide even more information about the code execution on different parts of a CPU [175]. Similarly to their power SCA attack on laptops, Genkin et al. used EM traces to extract encryption keys [64]. Sehatbakhsh et al. found the number of characters typed and even entire passwords typed on computers [193]. SoCs are also at risk; Longo et al. focused on the AM335x SoC's CPU, cryptographic coprocessor, and the NEON single instruction multiple data (SIMD) coprocessor, and addressed the challenges of collecting CPU traces, while accounting for interrupts and synchronization issues [123]. Their analysis highlights the difference in leakage among the SoC components, while demonstrating the feasibility of the attack.

Understanding and quantifying the information leakage can enable more effective attacks and facilitate the quest for countermeasures [229]. In their work on side-channel-aware software engineering, McCann et al. described a technique for modelling data-dependent leakage from instructions [139]. The knowledge of the sources of leakage permitted Primas et al. to break the security of a lattice-based encryption scheme running on an ARM Cortex-M4F CPU, using only a single trace obtained by combining the leakage of the entire decryption process [168].

Neural networks too are not immune to EM-based SCA. Assuming an attacker who can send inputs to the target device, Batina et al. used correlation analysis to recover the weights of an NN, along with a combination of simple and differential analysis to find the number of its layers and weights; their targets were a decapsulated ATmega328P processor and an ARM Cortex-M3. For inferring the activation function, however, they relied on a timing side channel [17]. Soon

after, Takatoi et al. showed how to find the activation function using simple EM analysis [205]. Robyns et al. used CNNs for another purpose—to classify EM traces corresponding to various encryption instructions of a NodeMCU device [183]. In SCANDALee, Strobel et al. chose to attack PIC16F687, in which most of the instructions take four clock cycles to be executed, making the task of identifying the boundaries between them significantly easier [204]. Polychotomous linear discriminant analysis was used for preprocessing to emphasize the particularly distinctive features in the observed data, classified by a k-nearest neighbors classifier. The authors reported recognition rates of 96% on test data and 88% on real code. However, their measurement setup required decapsulation of the target device, leaving physical traces of the attack. Decapsulation is not always a requirement; e.g., Vaidyan and Tyagi collected the EM emanations from an Atmega328 processor without decapsulating the IC [213].

4.2.2 Software-Based Side-Channel Attacks. For power efficiency, modern CPUs typically provide users with software access to power consumption information and control of the associated parameters. This leads to software-based side-channel exploits, ④ in Figure 5. Yan et al. collected power information from the battery management unit (BMU) on smartphones, allowing application identification, user interface inference, password length guessing, and geolocation estimation, all of which constitute user security breaches [225]. Qin and Yue proposed a power estimation method based on SVMs and requiring no root privileges. They used it for website fingerprinting on Android 7 [172].

It is important to note that side-channel security is not guaranteed by TEEs: O'Flynn and Dewar successfully leveraged the on-board analog-to-digital converter on a Cortex-M processor, with TrustZone, for remote SCA across security domains [164]. Intel devices are similarly vulnerable: By reading Intel running average power limit (RAPL), Mantel et al. could distinguish between different RSA keys [134]. Lipp et al. showed the feasibility of power SCA on x86-powered laptops and servers, based on unprivileged access to the RAPL [118]. Their *PLATYPUS* exploits compromise the security of Intel SGX enclaves, as an unprivileged adversary can leak AES-NI keys, while a privileged one can recover RSA keys. Even the less expected interfaces can facilitate exploits; Gravellier et al. demonstrated the risks associated with allowing software access to delay-line components on SoCs [76]. They used delay-locked-loops and programmable delay-blocks, implemented in memory controllers for the alignment of the sampling clock and the data signals, to carry out a CPA attack against OpenSSL AES-128 on two SoCs (both with ARM processors).

4.2.3 Countermeasures. An effective software countermeasure involves automated code modification; however, it comes at a cost of decreased performance and increased memory requirements [19, 219]. Alternatives are lightweight cryptographic primitives, more efficiently masked [78, 167], or random code injection for obfuscation [225].

Decreasing the leakage from the hardware itself typically requires its redesign. De Mulder et al. integrated defenses into the hardware architecture of a soft-core RISC-V processor and validated them on a Zynq FPGA; to reduce the leakage, they implemented masking in the CPU and added a protection for the memory accesses [156]. PARAM is another instance of a side-channel hardened microprocessor, implemented and evaluated on a SASEBO-GIII FPGA [56]; the authors first analyzed the RTL of a RISC-V processor to identify leaky modules and then applied obfuscation to reduce leakage in the datapath and hide the addresses sent to the cache. Finally, restricting access to the power-reporting interfaces or limiting their measurement resolution (time or energy) can hinder software-based exploits [118].

# 4.3 Fault Injection

Instead of monitoring the emanations from a CPU, an attacker with hardware access can inject errors in the operation of the CPU. Moreover, recent efforts to reverse-engineer the DVFS interfaces on modern processors opened the way for fault injection via software access only. In what follows, we present exploits with both access models (Figure 3).

Manuscript submitted to ACM

4.3.1 Hardware-Based Fault Injection. An attacker with physical access to the victim can change the voltage supply or the clock frequency, or inject glitches. The goal may be to fault CPU operations or crash the software, e.g., through a fault injected into the opcodes of the executed instructions. Alternatively, the attacker may want to gain information from the results of the faulty computations, in which case access to the victim's outputs is typically required.

Voltage. Manipulating the supply voltage to affect the operation of processors, ⑥ in Figure 5, has long been investigated. Barenghi et al. studied the effects of undervolting an ARM9 CPU with a 5-stage pipeline [14]. They found that only the LOAD instructions were affected, due to their long datapaths, resulting in two possible errors: instruction swapping and data loading. In the first case, the fault occurs during the instruction load or the evaluation of a branch condition, resulting in a wrong instruction being loaded. In the second case, the loaded data is faulty. Barenghi et al. used undervolting against AES, knowing that the faults would be injected in the values loaded from memory and leveraging them for a differential fault analysis (DFA) attack [14]. Additionally, they attacked the RSA signature and encryption primitives, and managed to recover the private key through a single faulty signature and enable decrypting an RSA message when in possession of one faulty and one correct encryption of the same unknown message [14].

Carefully choosing the fault injection parameters, e.g., the glitch amplitude, duration, and the number of occurrences, can make the difference between a successful and a failed exploit. Carpi et al. tested various strategies for finding successful attack parameters on smart cards [35]. Bozzato et al. proposed a new voltage fault-injection setup to generate arbitrary voltage glitches [27], and used it to extract the firmware of six different microcontrollers, by attacking the commands that give read access to the adversary.

Voltage-based fault injection can be exploited for other purposes as well. Timmers and Mune injected glitches in the power supply line to fault the U-Boot of an ARM processor and load attacker-controlled values into the program counter register [209]. With glitch-injected faults, they also managed to access physical memory addresses and escalate privilege levels. Spruyt et al. proposed using fault injection in a manner similar to SCA; they injected faults into the victim circuit and turned the observed faults into probability traces, which are correlated with the power consumption [199]. Cojocar et al. showed that some of the common countermeasures, e.g., instruction duplication and *n*-plication, are not effective against fault injection attacks on ARM Cortex-M4 processors [42].

Most recently, hardware fault injection was used against a "full-fledged Intel CPU": Chen et al. reverse-engineered how the voltage level is controlled on Intel processors [37]. In their so-called *Voltpillager* attack (⑦ in Figure 5), the authors used the serial voltage identification (SVID) bus, on which they connected a microcontroller-based system, to send the required voltage value to the voltage regulator. Chen et al. demonstrated some faults in the elementary operations (e.g., delaying writes from the memory to the cache) and showed the same proof-of-concept attacks as the remote *Plundervolt* attack (discussed later in this section). Intel's current mitigations against Plundervolt are ineffective against Voltpillager, as the latter has a stronger access model. TEEs are not effective either, as they do not provide tight-enough security guarantees in such a threat model [37].

Frequency. Fault injection is possible by changing the frequency of the processor's clock, (§) in Figure 5, or by injecting clock glitches. Bar-El et al. showed that clock glitches can be leveraged to skip instructions, and hence to execute a subset of program instructions, as well as to corrupt the processed data [13]. Korak and Hoefler studied the effects of clock glitches on an ARM Cortex-M0 and an ATxmega 256, and proposed the combination of voltage and clock glitches to improve the reproducibility of the injected faults [107]. For a higher success rate and to get a larger time window for the fault injection, Korak et al. combined heating with clock glitches [108]. Injected faults are not always easy to exploit; looking at 8-bit microcontrollers, Balasch et al. highlighted the complexity of exploiting injected

faults, because they may affect two stages of the pipeline at the same time, whereas which stages are affected depends on the parameters of the clock glitch [12].

The design of a glitch injector is essential for the attack success. Kazemi et al. proposed two clock glitch generators, both implemented on an FPGA, and used them to fault an ARM Cortex-M3 microcontroller running an AES encryption [98]. Obermaier et al. proposed a *fuzzy glitch* based on ring oscillators (ROs) and used it to inject faults into an ARM Cortex-M0 microcontroller [160]. Using phase-locked loops (PLLs) to generate the clock signal from an external clock source does not provide enough protection against clock glitches; Selmke et al. managed to force the PLL to overclock using high-frequency signals [195]. Since the PLL generates the internal clock signal by modifying the input clock signal (multiplying or dividing the frequency by a factor), changing the frequency of the external clock for enough clock cycles will result in the PLL also adjusting its output clock signal.

EM Field. Instead of manipulating the voltage supply to inject faults, an attacker can channel high amplitude voltage pulses through an EM probe, ① in Figure 5. The generated EM pulses can lead to timing constraint violations or (re)setting of flip-flops [161]. Manipulating the IC itself can affect the fault injection; Schmidt and Hutter compared the errors induced in a microcontroller when it is encapsulated, front-side decapsulated, and back-side decapsulated [191]. For a nearby probe, front-side decapsulation resulted in the highest injected current. For a probe further away, no difference among the three scenarios was observed. Dehbaoui et al. confirmed that EM fault injection can work without tampering with the victim device, by carrying out a DFA attack against an AVR microcontroller running AES encryption [46].

Moro et al. built a basic fault model for an ARM-Cortex M3, while investigating the effects of the probe's position and the timing of the pulses [151]. Trouchkine et al. used EM pulses to characterize fault-injection effects on a BCM2837 (ARM) and an Intel Core i3, to determine which type of the fault occurs (memory corruption, register corruption, or bad fetch) and which microarchitectural block is affected (the registers, cache, pipeline, memory management unit, or the bus) [210]. Maldini et al. went one step further and optimized the parameters of the exploit with an evolutionary algorithm [132]. Menu et al. exploited the localized effects of the EM-fault injection (against data transfers from the flash memory to the data buffer of a Cortex-M microcontroller) to (re)set key bytes, carry out a DFA attack, and inject faults that persist until reboot, ultimately recovering the secret AES key [141].

The EM fault injection can be used for a variety of attacks: Rivière et al. targeted the instruction cache of an ARMv7-M architecture to steer its control flow, achieving a high reproducibility rate [182]. Elmohr et al. demonstrated multiple instruction faults and skips on a RISC-V processor and an ARM Cortex M0 [53]. Cui and Housley proposed leveraging second-order effects of EM fault injection, where a fault in one component can affect other components, to overcome the inability to use first-order effects (EM field injects faults into a specific component due to proximity) in modern processors, which run at frequencies higher than 1 GHz [44]. Their approach caused software execution to enter into a data-dependent fault condition that is normally unreachable on a TrustZone-equipped Internet protocol phone. Dehbaoui et al. employed EM-induced faults against the round counter of an AES implementation on an ARM Cortex-M3 processor, to induce another execution of the penultimate round; this allowed for a DFA attack with only two pairs of correct and faulty ciphertexts [47].

4.3.2 Software-Based Fault Injection. Until recently, manipulating the voltage or frequency supplied to a processor required having physical access to the device. This no longer holds, because researchers have reverse-engineered and discovered how to use DVFS interfaces of modern Intel and ARM CPUs to carry out software-based attacks. These attacks take advantage of the separation of the energy management from security, as DVFS interfaces can allow a Manuscript submitted to ACM

user to lower the voltage or increase the frequency to a point where correct operation can no longer be guaranteed. The research we survey here targets TEEs, which can protect against other attacks (e.g., RowHammer attacks) [157]. In this subsection, we focus on the attacks which do not lead to DoS; however, it should be noted that the incorrect CPU operation resulting from these exploits may still be manifested as device unresponsiveness or lock (e.g., for a ransom) [159]. The five generic steps of DVFS-based attacks are as follows [173, 174, 206]:

- (1) Environment setup: setting up the initial voltage and frequency (which cause no faults) and clearing the residual states, which could affect the attack. These states include the cache and the branch prediction table contents, cleared by flushing the cache and running the target threads (the victim and the attacker) multiple times. The system interrupts can be disabled to avoid any external interference.

- (2) Profiling for an anchor: determining when the victim code starts executing, through software monitoring or cache side channels.

- (3) Pre-fault delaying: delaying the fault injection until the execution of specific victim instructions, to carefully tune the fault injection for exploitable hard-to-detect errors. The delay depends on the processor frequency (known to the attacker) and the executed instructions (known when targeting a standard encryption algorithm).

- (4) Fault injection: lowering the voltage or increasing the frequency to inject the desired fault.

- (5) Restoring the original voltage and frequency: restoring the normal operation of the victim.

Frequency. In 2017, Tang et al. demonstrated the first DVFS-based attack on ARM TrustZone [206]. In this so-called CLKSCREW attack, in Figure 5, the adversary increases the frequency of the processor beyond the correct operation limits. The resulting faults were used to extract secret cryptographic keys from TrustZone and to escalate the privileges of a malicious kernel driver, on an ARMv7 processor inside an Android mobile device. The authors created a custom kernel driver, which launches separate threads for the attacker and the victim codes, and pins each thread to a separate core. On ARM processors, different cores can have different frequencies, and hence, the attack frequency is not restricted by the effects it may cause to the adversary core. No similar attacks have been demonstrated on Intel CPUs, as many of them do not support overclocking [174].

Voltage. DVFS interfaces control the frequency and the voltage, ① in Figure 5. Targeting an ARMv7 processor with TrustZone, the VoltJockey attacker extracts cryptographic keys and faults the RSA signature verification, using a malicious kernel module [173]. Even though the voltage is the same for all cores, given that the frequency can be different, it is possible to ensure that only the victim core experiences faults. The vendor-specified operating performance points (OPPs)—specific voltage and frequency combinations to guarantee correct operation of the processor—pose no restriction for the attack, as the frequency and voltage regulator drivers can modify the frequency and voltage at the request of the top-level software. To avoid the limitation of the defined voltage threshold in the regulator property description file, the VoltJockey authors modify the voltage probe function in the voltage regulator driver. As an extension of their work on ARM TrustZone, Qiu et al. demonstrated the VoltJockey attack on Intel SGX [174]. Similarly, Murdock et al. and Kenjar et al. presented the Plundervolt and Voltpwn exploits [99, 157]. The three works targeted some cryptographic code as part of their proof-of-concept (AES for Plundervolt and VoltJockey). The adversary requires root privileges over the system, which is not inconsistent with the use of SGX enclaves, which normally protect against processes at a higher privilege level. The main difference with respect to the TrustZone exploit is that the voltage and frequency are shared among the cores. If not carefully controlled, the low voltage may result in a kernel panic, leading to the system freezing or rebooting [174]. The voltage is controlled through an undocumented Intel model specific register

(MSR); bits of MSR 0x150 can be changed, representing the desired voltage offset, and specifying to which planes the voltage change is applied (CPU core, GPU, cache (core), uncore or analog I/O) [157]. Techniques such as SGX-Step [31] can be used to carefully control the fault injection against the enclave [157]. Murdock et al. investigated the voltage decline time, the possibility of faulting multiplications inside the enclave, overvolting, and differences among CPUs. Plundervolt was also used to cause the memory safety violations, through faulty imul instructions, leveraged to redirect the trusted white list into the attacker-controlled memory [157].

Kenjar et al. added an offline analysis step to test the operational limits of a processor similar to the target [99]. They also added a step to analyze the cores of the target system to determine the fault pattern and find an advantageous placement for the victim. The environment setup step included disabling the operating system drivers which communicate with the hardware interfaces for changing the voltage, and disabling the automatic hardware-based selection of the voltage and the clock frequency. Finally, Kenjar et al. introduced the concept of *stressors*—pieces of code running on the logical partner of the victim's core to increase the resource contention and the core temperature, for an improved likelihood of fault injection. Hadjilambrou et al. [82] and Kim and John [103] show that highly effective stressors can be automatically generated using genetic algorithms, for the purpose of an attack or voltage noise characterization on CPUs.

4.3.3 Countermeasures. Processors typically handle load transients by detecting core voltage droops and then decreasing the working frequency [57]. Razor latches inserted in the pipeline are also helpful; they sample the output with two phase-shifted clocks, to detect discrepancies and repeat computations to fix them [55].

Checking for faults and attempting to recover from them works regardless of how the fault was injected (software or hardware interfaces). Aumüller et al. developed a software countermeasure for the RSA signature on a smart card with no hardware countermeasures [9]. They relied on the fact that voltage spike-induced faults can be injected into any value, except those from a read-only memory, which can be used to check computation correctness. Redundancy is one of the most common fault detection and recovery defenses. Moro et al. evaluated two software-based countermeasures against EM-fault injection, both aiming to detect or tolerate single faults, or specifically those which can cause instruction skipping [152]. One countermeasure repeats the instructions, while the other executes an instruction twice, storing the results in different registers and then comparing them. Both defense strategies improve the security for their specific use cases (a subset of instructions to protect or only protecting against instruction skipping), but do not render the executed code fully secure. Making the exploitation of the fault-injection interfaces (e.g., DVFS) more difficult for the adversary is also a possibility; in response to the software-based fault injection against SGX, Intel has disabled the overclocking mailbox interface configuration [157]. The perfect countermeasure does not exist, but the system designers and programmers can choose to deploy some of the available countermeasures for security-sensitive code.

# 5 ELECTRICAL-LEVEL ATTACKS ON FPGAS

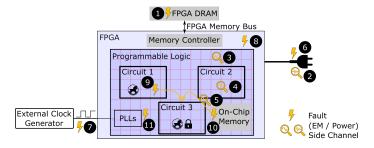

FPGAs, being both a prototyping platform and an acceleration platform, have received considerable attention from the hardware security community. Similar to CPUs, electrical-level attacks are applicable to FPGAs. In particular, the low-level programmability of FPGAs allows adversaries to exploit the electrical phenomena for their attacks [144]. We denote here the attacks carried out via the bitstream (i.e., FPGA configuration file) as software-based; the bitstream file is used to program the basic hardware blocks of the FPGA and have them obtain desired functionality. In addition to software-based attacks, we survey and discuss the attacks that target soft processors, common in embedded FPGAs. We show an example of an FPGA-based system, with highlighted vulnerable interfaces in Figure 6.

Fig. 6. An illustrative FPGA-based system, with highlighted electrical-level vulnerabilities.

#### 5.1 RowHammer

While the experimental setup by Kim et al. for studying RowHammer bitflips was based on FPGAs [102], for a long time, it was CPUs that RowHammer attacks were targeting. Recently, however, Weissman et al. examined whether FPGAs could be used for accelerating RowHammer exploits [224]. To that purpose, they used an Intel Arria 10 programmable acceleration card [8]. Their FPGA-based RowHammer attack, termed JackHammer, turned out to be significantly faster than the RowHammer exploit launched from the CPU, because FPGAs do not need to flush the memory addresses. The attack targeted a WolfSSL RSA application, running on the host CPU. While in JackHammer the FPGA acts only as the enabler of the exploit, the fact that it can induce faults in the shared memory means that FPGAs can also be the victims of JackHammer attacks; we underscore this exploit as ① in Figure 6.

5.1.1 Countermeasures. The most effective countermeasures against RowHammer, which would protect even against an FPGA-based attacker, are those implemented in the DRAM or the memory controller. Other countermeasures which rely on the software running on the CPU are not suitable, unless they are adapted to work on the FPGA's hardware [54]. In the absence of hardware performance monitors on the Arria 10 platform, Weissman et al. proposed implementing them on the FPGA [224]. Elnaggar et al. used a monitor on the FPGA fabric to detect attempts to launch RowHammer exploits [54]. Weissman et al. also proposed defense mechanisms specific to the tested platform; the current version of Open Programmable Acceleration Engine (OPAE), used on the Arria 10 platform, makes physical addresses available to the user space, and allows for huge pages. Disabling huge pages and virtualizing the addresses would render finding eviction sets considerably harder, thus improving the system security. Algorithmic-level patches may also be useful to protect against the fault injection attacks against RSA [224]. However, without these countermeasures actually being deployed and evaluated, the security of current systems against RowHammer remains questionable.

#### 5.2 Side-Channel Analysis

Many side-channel exploits have been demonstrated on FPGAs, most often relying on the attacker having hardware access to the victim device. However, hardware-security researchers have recently taken advantage of the programmability of FPGAs to carry out remotely-controlled side-channel attacks, targeting the FPGAs hosted by the cloud service providers. In the following subsections, we discuss both types of exploits.

5.2.1 Hardware Side-Channel Attacks. Similar to the exploits against CPUs, an attacker with access to the hardware can measure the power consumption or the EM emanations from an operational FPGA, and gain information about the algorithm executing on the device.

Power. Power side-channel attacks against FPGAs, ② in Figure 6, were first demonstrated in 2003 [162]. Soon after, Standaert et al. examined how DPA differs when applied to FPGAs versus CPUs [200]. Since then, many works have successfully demonstrated hardware SCA on FPGA implementations of cryptographic algorithms [20], sometimes helped by hardware Trojans [114, 117]. Researchers also looked at how to optimize the side-channel exploits, for example by finding the optimal linear transform to apply to the traces, to more easily distinguish the correct key [163]. Yao et al. demonstrated SCA on a masked AES executing on a soft RISC-V processor, implemented on a Xilinx Spartan-6 FPGA [226]. At first, they collected the side-channel traces to distinguish between various algorithmic steps (e.g., mask generation or encryption). Then, with a carefully controlled clock glitch fault injection (🗇 in Figure 6), they managed to disable the mask and recover the secret key using standard first-order SCA. FPGA cryptographic circuits are not the only targets of the power SCA attacks. The encrypted bitstreams, which should protect the confidentiality of proprietary designs, are vulnerable as well; Moradi et al. successfully broke the bitstream encryption of an Intel Stratix-II and a Xilinx Virtex-II FPGA through power SCA, where power measurements are facilitated by inserted resistors on the paths of interest [148, 149]. While power-analysis exploits focus on the dynamic power consumption, Moradi used static power consumption against AES FPGA implementations with masking and shuffling countermeasures [147]. Even though the attack is feasible, the signal-to-noise ratio (SNR) of the static power is considerably smaller than that of the dynamic power, thus requiring a particular measurement setup. Furthermore, the adversary model is much stronger, assuming control over the clock signal. Finally, while not targets for disassembly, FPGAs can be programmed to implement softcore processors. Power traces collected in that case allow for side-channel disassembly [113].

Today, FPGAs are commonly used for accelerating ML algorithms, which are an attractive target for the attackers. Wei et al. carried out a power SCA on a convolutional neural network (CNN) implemented on the SAKURA-G FPGA board [222]. After collecting power traces, they applied a noise-removal technique and then carried out two input-recovery exploits. The first one assumed a passive adversary who tries to distinguish pixels which are part of the input image background. The second one assumed an adversary capable of sending inputs to the target, for profiling purposes, who, using prebuilt power templates, tries to recover the pixels of the input image [222]. Dubey et al. used DPA to extract the binary neural network (BNN) model parameters (weights and biases) [49]. Besides being the targets, ML algorithms are enablers of the exploits: Mukhtar et al. used ML to recover the secret key of an elliptic curve cryptography algorithm running on a Xilinx Kintex-7 FPGA [154], while Wang and Dubrova combined several CNN classifiers to reduce the number of traces necessary to recover the AES encryption key on Artix-7 FPGAs [220]. Ramezanpour et al. used unsupervised learning against AES [178], while Aydin et al. leveraged deep learning for breaking the lattice-based key-exchange protocols [11].

EM Field. EM emanations are also useful for side-channel analysis on FPGAs [34]. Carlier et al. and De Mulder et al. used the EM SCA, ③ in Figure 6, to attack an AES FPGA implementation [34] and break the security of an FPGA implementation of an elliptic curve cryptosystem [155], respectively. Similarly, Kim et al. carried out the power and EM SCA on the ARIA block cipher running on an Intel APEX 20K FPGA [100]. Investigating the strengths and limitations of the EM SCA, Heyszl et al. showed that the SNR changes with the location of the EM probe; due to local leakage, better attack results can be obtained if the probe is positioned over the target part of the design after a profiling phase [86]. Hori et al. carried out correlation-based SCA against an AES running on Xilinx Kintex-7 and Virtex-5 FPGAs [88]. With the smaller technology node of the Kintex-7 family, fewer traces were required for the full recovery of the cryptographic key. The SNR of subkeys at some locations was different than at others, indicating that the structure of the circuit does affect the attack success [88]. Bitstream encryption is vulnerable to EM side-channel analysis: Moradi and Schneider Manuscript submitted to ACM

demonstrated the attack feasibility on Xilinx series 4, 5, 6, and 7 FPGAs [150]. ML algorithms also fall victim to EM SCA: Yoshida et al. used correlation EM analysis to recover the weights of an MLP, under the assumption that the adversary has control over the inputs to the MLP [230].

5.2.2 Software-Based Side-Channel Attacks. By carefully programming the FPGA logic, a malicious party can implement an on-chip sensor for measuring the core voltage variations or the crosstalk-coupling between neighboring long wires. These software-defined sensors are the enablers of remotely-controlled attacks, targeting cloud FPGAs.

*Power.* Remote power-side channel attacks, ④ in Figure 6, commonly employ sensors based on ring oscillators (ROs), easily created by connecting an odd number of inverters in a loop. The RO frequency of oscillation depends on the loop delay, which, in turn, depends on the power supply voltage. To monitor its variation with time, it is sufficient to connect the RO output to the clock input of a frequency counter and to sample the counter output at fixed periods of time.

Zick and Hayes were among the first to use ROs for monitoring on-chip variations [238]. To minimize the sensor footprint, they employed residue number system ring counters using shift register look-up tables (LUTs), resulting in only 8 LUTs per sensor on a Xilinx Virtex-5 FPGA. On a Zynq-7020 SoC, Zhao and Suh showed that ROs are the enablers of side-channel attacks against RSA cores and CPUs on the same SoC [236]. Their insight was that power side channel allows for distinguishing the CPU activity levels, suitable for timing-based attacks against RSA exponentiation operation which executes in constant time. One drawback of RO sensors is that, to obtain good measurement resolution, the sampling period of their frequency counter should be hundreds or even thousands of clock cycles. To address this limitation, Gravellier et al. combined high-frequency ROs with Johnson ring counters [75].

As an alternative to limited-resolution RO sensors, Zick et al. proposed delay line-based time-to-digital converters (TDCs), capable of sensing nanosecond-scale voltage transients on FPGAs [239]. Many subsequent works employed TDCs: Schellenberg et al. used TDCs for a CPA attack against an AES FPGA core [189] and for an inter-chip power side-channel attack [190], showing that remote attacks are not limited to a single chip only.

Remote side-channel exploits have been demonstrated in cloud setting as well. Glamočanin et al. were the first to demonstrate a successful power SCA attack against an AES core, using TDCs, on Amazon AWS F1 instances [71]. More recently, Moini et al. used TDCs to recover the inputs to a BNN, under the assumption that the adversary knows the BNN structure [146]. Zhang et al. used TDCs to remotely steal the structure of an FPGA neural network [234].

EM Field. The possibility of remote measurement of the EM field emanated from an FPGA core is an open research question. However, the effects of the EM coupling between neighboring FPGA wires (⑤ in Figure 6) can be measured remotely; it has been shown that the EM coupling between neighboring FPGA wires can leak information about the logical level carried by the observed wire [60, 69]. Ramesh et al. used an RO-sensor to learn the AES final round key. First, they ensured that the RO is routed next to one of the long wires carrying inputs to the final round Sbox. Then, with the observed ciphertext (assumed to be publicly available) and the oscillation count of the RO, they examined all the possible values for the target key byte until finding one consistent with the obtained measurements [177]. Giechaskiel et al. showed that a variety of RO-based crosstalk-coupling sensors can be successfully deployed on cloud FPGAs, while bypassing the checks for combinational loops put in place by the cloud service providers [67].

5.2.3 Countermeasures. Protections against side-channel analysis on FPGAs focus on decreasing the information leakage or preventing remotely-controlled attacks, by disallowing sensor circuits or better isolating the neighboring designs. Two common techniques for decreasing information leakage are hiding and masking [133]. In hiding, the goal is to reduce the SNR available to the adversary. In masking, the data processed by the circuit is obfuscated, so that

the observable leakage is independent of the secret [181]. Implementing these techniques incurs considerable area or frequency penalties. Furthermore, the circuit can still remain vulnerable to more advanced, higher-order attacks [133].

Le Masle et al. used a network of on-chip RO sensors and a proportional-integral-derivative controller to monitor and maintain an approximately constant core voltage, effectively reducing the SNR [135]. As actuators, they employed long routing wires (equivalent to high capacitive load). In a similar direction, Krautter et al. used a TDC sensor to control a noise-generating *fence* composed solely of ROs [110].

Güneysu and Moradi proposed and evaluated a set of countermeasures against DPA on FPGAs [81]: They generated Gaussian noise by leveraging shift register LUTs, BRAM write collisions, and short circuits in the switch boxes. They randomized the clock signal to impede data alignment and implemented a circuit to detect if the external clock is manipulated. Finally, they proposed scrambling the contents of Sboxes or Tboxes. These countermeasures were tested on an AES core in Xilinx Virtex-II Pro.

Sasdrich et al. proposed leveraging the dynamic reconfiguration capability of FPGAs to dynamically change the hardware implementation of a PRESENT cipher and thus improve the resistance against SCA exploits [187]. Dubey et al. investigated the application of masking and hiding to a BNN, demonstrating improved security but also highlighting the challenges of building a fully side-channel resistant neural network [49].

To detect FPGA sensors, Krautter et al. [112] and La et al. [115] developed bitstream scanners, which reconstruct the design netlist and search for so-called *signatures* of potentially malicious circuits. However, the developed scanners target only a subset of FPGA families: the Lattice iCE40 [112] and the Xilinx Ultrascale+ [115].

Mitigating crosstalk side channels was first addressed by Huffmire et al. who proposed using *moats* (guard bands between design partitions) for spatial separation and *drawbridges* for routing core-to-core communication signals and isolating them [92]. Yazdanshenas and Betz proposed wrapping user applications into soft shells and encrypting incoming and outgoing data [228]. Compared to unencrypted traffic, they report up to 80% higher latency and a 20% decrease in the available user area. Luo et al. developped HILL, a hardware isolation framework, which places security-critical nets in the center of a core, routes them without using the long wires and isolates them from other FPGA cores [127]. Seifoori et al. improved the FPGA compilation to ensure that the post place and route designs are protected by construction, i.e., that no untrusted signal is routed close to a security-critical net [194].

## 5.3 Fault Injection

An adversary with hardware access to an FPGA can externally inject faults. Moreover, the programmability of FPGAs allows for injecting faults internally. We discuss both scenarios below.

#### 5.3.1 Hardware Fault Injection.

Voltage. FPGA circuits are sensitive to both undervolting and overvolting [33](⑥ in Figure 6). Undervolting increases circuit delays, leading to timing violations, whereas overvolting glitches cause transient oscillations in the internal voltage, while trying to recover a nominal voltage value, ultimately resulting in transient undervolting [241]. Bhasin et al. evaluated the effects of undervolting on several AES implementations and observed that, when no countermeasures are implemented, the hardware with the lowest area is also the most vulnerable to differential fault analysis [21]. Zussa et al. investigated the mechanism of injecting faults into FPGA circuits through voltage glitches and concluded that it is the same as with clock glitches [241].