총 설

# 구리 전해 도금을 이용한 실리콘 관통 비아 채움 공정

김회철 · 김재정<sup>†</sup>

서울대학교 화학생물공학부 08826 서울특별시 관악구 관악로 1 (2016년 8월 31일 접수, 2016년 9월 21일 수정본 접수, 2016년 9월 22일 채택)

## Through-Silicon-Via Filling Process Using Cu Electrodeposition

Hoe Chul Kim and Jae Jeong Kim<sup>†</sup>

School of Chemical and Biological Engineering, Institute of Chemical Process, Seoul National University, 1, Gwanak-ro, Gwanak-gu, Seoul, 08826, Korea

(Received 31 August 2016; Received in revised form 21 September 2016; accepted 22 September 2016)

## 요 약

반도체 배선 미세화에 의한 한계를 극복하기 위해 실리콘 관통 비아(through silicon via, TSV)를 사용한 소자의 3차원 적충에 대한 연구가 진행되고 있다. TSV 내부는 전해도금을 통해 구리로 채우며, 소자의 신뢰성을 확보하기 위해결함 없는 TSV의 채움이 요구된다. TSV 입구와 벽면에서는 구리 전착을 억제하고, TSV 바닥에서 선택적으로 구리 전착을 유도하는 바닥 차오름을 통해 무결함 채움이 가능하다. 전해 도금액에 포함되는 유기 첨가제는 TSV 위치에 따라 국부적으로 구리 전착 속도를 결정하여 무결함 채움을 가능하게 한다. TSV의 채움 메커니즘은 첨가제의 거동에 기반하여 규명되므로 첨가제의 특성을 이해하는 연구가 선행되어야 한다. 본 총설에서는 첨가제의 작용기작을 바탕으로하는 다양한 채움 메커니즘, TSV 채움 효율을 개선하기 위한 평탄제의 개발과 3-첨가제 시스템에서의 연구, 첨가제 작용기와 도금 방법의 수정을 통한 채움 특성의 항상에 관한 연구를 소개한다.

Abstract – Intensive researches have been focused on the 3-dimensional packaging technology using through silicon via (TSV) to overcome the limitation in Cu interconnection scaling. Void-free filling of TSV by the Cu electrodeposition is required for the fabrication of reliable electronic devices. It is generally known that sufficient inhibition on the top and the sidewall of TSV, accompanying the selective Cu deposition on the bottom, enables the void-free bottom-up filling. Organic additives contained in the electrolyte locally determine the deposition rate of Cu inside the TSV. Investigation on the additive chemistry is essential for understanding the filling mechanisms of TSV based on the effects of additives in the Cu electrodeposition process. In this review, we introduce various filling mechanisms suggested by analyzing the additives effect, research on the three-additive system containing new levelers synthesized to increase efficiency of the filling process, and methods to improve the filling performance by modifying the functional groups of the additives or deposition mode.

Key words: Through silicon via (TSV), Electrodeposition, Copper, Additive, Superfilling

## 1. 서 론

구리(Cu)는 1.67 μ $\Omega$ ·cm의 낮은 비저항을 가지고 있어 전자 소자에서의 우수한 신호 전달 속도를 보이고, 높은 일렉트로마이그레이션(electromigration) 저항을 바탕으로 소자의 신뢰성을 확보하기에 적합한 물질이다[1]. 특히 다마신(damascene) 공정을 통해 미세 배

선의 다층화가 가능하여 현재 반도체 배선 공정의 주 금속 물질로 사용되고 있다. 소자의 성능 향상을 위해서, 다층 배선의 형성과 동시에 배선의 폭을 감소하여 소자의 직접도를 높이는 연구가 요구된다. 하지만 미세 배선 형성을 위한 노광 기술의 한계, 확산방지층과 금속 씨앗층의 마진 감소로 인한 균일한 금속층 형성의 어려움, 그리고 배선의 미세화에 따른 결함 없는 구리 채움의 어려움 등으로인하여 배선의 미세화 공정은 기술적, 물리적인 한계에 도달하고있다. ITRS (international technology roadmap for semiconductor)는 DRAM (dynamic random access memory)에서의 하프 피치(halfpitch)가 2030년까지 7.7 nm에 도달할 것으로 예상하지만, 실질적으로 2024년에는 DRAM에서의 미세화 공정이 한계에 도달할 것으로 2024년에는 DRAM에서의 미세화 공정이 한계에 도달할 것

<sup>†</sup>To whom correspondence should be addressed. E-mail: jjkimm@snu.ac.kr

<sup>‡</sup>이 논문은 광운대학교 한 춘 교수님의 정년을 기념하여 투고되었습니다. This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

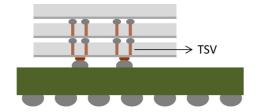

Fig. 1. Schematic diagram of stacked chips using TSV technology.

## 으로 예상하였다[2].

배선 미세화에 대한 한계를 극복하기 위해, 소자와 소자를 3차원 적으로 적층하는 연구가 각광받고 있다. 가장 주목받고 있는 연구로는 와이어 본딩(wire bonding)과 실리콘 관통 비아(through silicon via)를 이용한 기술이 있다. 와이어 본딩은 금(Au) 또는 구리로 구성된 와이어를 사용하여 칩(chip)과 외부를 연결하는 기술로, 와이어 형성을 위한 여유 공간이 필요하고 신호 전달 거리가 길다는 한계를 갖는다[3]. TSV는 실리콘 웨이퍼(wafer)를 관통하여 형성된 깊이약 50 µm 이상의 비아(via)로, Fig. 1에 나타나 있듯이 직접회로 (integrated circuit)와 직접회로를 전기적, 수직적으로 연결한다. TSV를 사용하여 최단 거리의 신호 전달이 가능하므로 와이어 본딩에 비해 높은 성능의 소자 패키징(packaging)을 구현할 수 있다[3]. TSV 적층 기술을 도입한 소자는 35% 이상 작은 크기, 40% 이하의소비 전력, 45% 이상의 단가 절감, 그리고 8배 이상의 대역폭 (bandwidth)를 가질 것으로 예상된다[2].

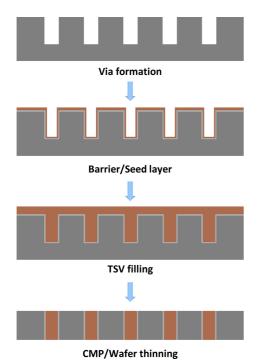

TSV는 Fig. 2에 나타나 있는 공정을 통하여 제작한다. 실리콘 웨이퍼에 사진(lithography)과 DRIE (deep reactive-ion etching) 공정을 거쳐 직경 수  $\mu$ m, 깊이 50  $\mu$ m 전후의 비아를 형성한다. 이후 구리가 실리콘 웨이퍼로 확산하는 것을 방지하기 위해 확산방지층(diffusion barrier layer)을 형성하고, 전해 도금을 진행하기 위한 금속 씨앗층 (seed layer)을 확산방지층 위에 순차적으로 형성한다. 확산방지층과

Fig. 2. Fabrication process flow for TSV.

Korean Chem. Eng. Res., Vol. 54, No. 6, December, 2016

씨앗층은 일반적으로 물리기상증착(physical vapor deposition)법을 이용하여 증착하나, 최근에는 무전해 도금을 통한 전착법도 활발하 게 연구되고 있다. 무전해 도금은 외부에서 제공하는 전자 없이, 기 판 표면에서 환원제가 산화되며 제공하는 전자를 금속 이온이 받아 자발적으로 환원되는 전착 방법이다. 무전해 도금을 이용하여 비전 도성 기판에서 금속을 전착할 수 있고, 물리기상증착법에 비해 높은 단차 피복율을 갖는 금속막 형성이 가능하다[4]. 무전해 도금으로 전착한 코발트(Co) 합금의 확산방지층은 400 °C의 어닐링(annealing) 에서 구리의 확산을 효과적으로 방지하며[5], 도금액 조성에 따라 다양한 특성의 확산 방지층을 무전해 도금으로 전착할 수 있다[6,7]. 구리 씨앗층 역시 무전해 도금으로 형성할 수 있고, non-vosch 타 입의 TSV와 같이 물리기상증착을 통해 균일한 씨앗층을 형성하기 어려운 구조에 무전해 도금을 적용하여 높은 단차 피복율의 균일한 씨앗층 형성이 가능하다[8]. 최근에는 무전해 도금을 이용하여 모든 배선 공정을 액상에서 진행하는(all-wet process) 연구가 각광을 받 고 있다[9]. 금속 씨앗층을 형성한 TSV 웨이퍼를 도금액에 침지한 후, 전압 또는 전류를 인가하는 구리 전해 도금으로 TSV 내부를 구 리로 채운다. 소자의 신뢰성을 확보하기 위하여 전해 도금을 통해 결함없이 TSV를 채울 것이 요구된다. 구리 전해 도금 이후 화학적 기계적 연마(chemical mechanical polishing) 공정으로 과전착된 구 리를 제거한다. 최종적으로 웨이퍼 thinning을 통해 배선 형성을 마 무리하고, TSV의 상단부와 하단부에 직접 회로를 연결하여 적층한다.

다마신 공정에서의 미세화와 마찬가지로, 소자의 직접도 향상을 위해 낮은 직경과 높은 종횡비의 TSV를 사용할 것이 요구된다. TSV 종횡비의 증가에 따라 결함 없는 채움을 위한 공정 난이도가 증가하므로, 결함 없는 채움을 위하여 구리 전해 도금과 유기 첨가 제에 대한 깊이 있는 이해가 선행되어야 한다. 본 총설에서는 다양한 첨가제를 이용한 TSV의 채움 결과와 채움 메커니즘(mechanism)에 대해 소개한다. 고종횡비 TSV 채움을 위한 3-첨가제 시스템에서의 최근 연구 동향을 살펴보고, TSV 깊이 방향으로의 위치에 따른 첨가제의 거동과 첨가제 사이의 상호 작용을 기반으로 TSV 채움 메커니즘에 대한 논의를 진행한다. 또한, 채움 특성을 개선하기 위한 첨가제의 개발 및 도금 방법의 개발에 대한 연구를 안내한다.

#### 2. 구리 전해 도금을 이용한 TSV 채움과 채움 메커니즘

## 2-1. 첨가제를 사용한 구리 전해 도금

구리 전해 도금은 외부에서 전자를 제공하여 전도체 표면에 구리 이온을 구리로 환원시키는 방법이다. 구리 씨앗층까지 형성한 TSV 기판을 작업 전극으로 사용하고, 구리 전극이나 불용성 전극을 상대 전극으로 사용하여 각 전극을 도금액에 침지한 후, 전압 혹은 전류를 인가하면 TSV 기판에서 구리 환원이 진행된다. 그와 동시에 상대 전극에서는 구리의 산화, 도금액 내 조성물의 산화 반응 등이 진행된다[10]. 도금액은 구리 이온을 제공하기 위한 구리 화합물, 도금액의 저항을 낮추기 위한 지지전해질 등으로 구성되며, 유기첨가제의 흡착을 돕기 위해 소량의 염화 이온이 기본적으로 도금액에 포함된다[10]. 대표적으로 황산구리(CuSO<sub>4</sub>)와 황산(H<sub>2</sub>SO<sub>4</sub>)이 각각 구리 화합물과 지지전해질로 사용되고 있다. 메탄술폰산 (methanesulfonic acid)은 황산에 비해 구리 화합물의 용해도가 높은 지지전해질로, 고농도의 구리 이온 도금액을 이용한 TSV 채움 연구에 적용되고 있다[11].

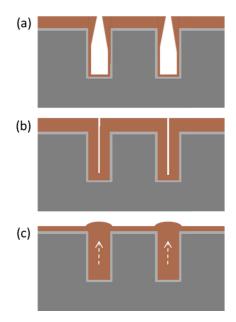

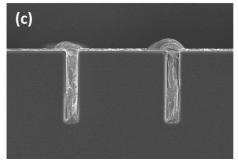

Fig. 3. Three types of deposition profile during the TSV filling. (a) Subconformal, (b) conformal, (c) superconformal deposition.

전해 도금을 이용한 TSV의 채움 시 발생하는 3가지의 전착 형태가 Fig. 3에 나타나 있다. 유기 첨가제 없이 도금을 진행하거나, 혹은 높은 전류를 인가하는 경우, TSV의 구조적인 특징으로 인하여 전기장이 TSV의 입구에 집중되고 핀치 오프(pinch-off) 효과, 또는 비등각(subconformal) 전착을 야기한다[12]. 구리 이온이 TSV 입구에서 우선적으로 환원되므로 입구 막힘으로 인해 보이드(void)가형성된다. 구리 전착이 TSV의 입구, 벽면, 그리고 바닥에서 동일한속도로 진행될 경우, 등각(conformal) 형태의 결과를 보이며 심(seam)이 형성된다. 보이드 또는 심과 같은 결함은, 소자의 반복 작동이나 어닐링(annealing) 이후 구리 금속 내부의 스트레스가 완화되는 과정에서 크기가 확장한다[13,14]. 결함의 성장으로 인한 소자의신뢰성 저하를 방지하기 위해, TSV의 입구에서는 구리 전착을 억제하고 TSV 바닥에서만 구리 전착을 강제하는 바닥 차오름(bottom-up) 채움, 즉 초등각(superconformal) 전착 혹은 수퍼필링(superfilling)을 통해 결함 없이 TSV를 채울 것이 요구된다.

구리 전해 도금에 사용하는 유기 첨가제는 구리 전착 속도를 국 부적으로 조절함으로써 바닥 차오름을 유도한다. 첨가제는 구리 전 착 속도를 가속하는 가속제(accelerator), 전착 속도를 억제하는 감 속제(suppressor), 그리고 표면 단차를 제거하여 평탄한 도금막을 형성하도록 도와주는 평탄제(leveler) 등으로 그 기능에 따라 분류 할 수 있다. 가속제로는 SPS (bis (3-sulfopropyl) disulfide), MPSA (3-mercapto-1-propanesulfonic acid), 혹은 DPS (3-N,N-dimethylamonodithiocarbamoy-1-propanesulfonic acid)가 대표적인 유기 화 합물로 알려져 있다[15-17]. 구리 전해 도금에 사용되는 가속제는 일반적으로 -S-S-의 이황화물(disulfide) 결합이나 -SH의 메르캅토 (mercapto) 작용기를 포함하고 있으며, 두 분자의 메르캅토가 산화 되어 한 분자의 이황화물 결합을 형성하고, 이러한 산화 과정에서 생성된 전자는 Cu²+이 Cu+으로 환원되는데 사용된다[18,19]. 구리의 전기화학적인 환원은, Cu<sup>2+</sup>이 Cu<sup>+</sup>으로 환원되고, Cu<sup>+</sup>이 Cu로 환원 되는 두 단계의 환원 반응을 거친다고 알려져 있으며, 가속제는 속 도결정단계인 Cu²+이 Cu+로 환원되는 첫 단계 반응을 촉진하여 전

체 환원 반응을 가속한다. 감속제로는 PEG (polyethylene glycol)와 PEG-PPG 공중합체(polyethylene glycol-polypropylene glycol copolymer) 등의 중합체 계열 유기 화합물이 대표적으로 사용된다. 감속제는 Cl<sup>-</sup> 혹은 Cu<sup>+</sup>-Cl<sup>-</sup> 형태로 구리 표면에 흡착한 염화 이온과 착물 (complex)을 형성하여 흡착하고, 구리 이온이 구리 표면에 접근하는 것을 물리적으로 방해하여 감속 효과를 보인다[20-22]. 평탄제는 구리 전착물의 돌출부에 우선적으로 흡착하여 돌출부에서의 구리 전착을 억제하는 동시에, 함몰부에서의 구리 전착을 유도하여 평탄한 구리 전착막을 만든다. 평탄제는 JGB (Janus Green B), PEI (polyethylene imine)과 같이 삼차 아민(tertiary amine) 혹은 사차 암모늄염(quaternary ammonium salt) 형태의 질소 원자를 포함하는 화합물이 주로 사용된다[23,24].

상기의 각 첨가제는 상호간에 경쟁적으로 작용하기 때문에, 첨가 제의 상대적인 흡착 거동을 고려하여 반도체 배선의 채움 과정이 설명되어 왔다. 미세 배선에서의 수퍼필링 현상을 설명하는 대표적인 이론인 CEAC (curvature enhanced accelerator coverage) 모델 역시 첨가제의 작용기구에 초점을 맞추어 채움 현상을 설명한다[25-28]. 전극을 도금액에 침지하는 순간 염화 이온은 빠르게 흡착층을 형성 하여 감속제의 흡착을 돕는다. 이후 구리 전해 도금을 진행하는 동 안 배선 내부에 흡착한 감속제는 서서히 가속제로 치환되며, 이는 순환전압전류법(cyclic voltammetry)의 전기화학분석에서 도금 시 간에 따라 구리 환원 속도가 증가하는 것을 통해 규명되었다[29]. 배선 내부에서 구리 전착이 진행됨에 따라 면적이 감소하며, 단위 면적 당 가속제의 표면 농도가 상대적으로 증가하는 축적(accumulation) 현상이 진행된다[27]. 배선 바닥에서 축적된 가속제는 바닥 차오름 을 유도하여 종국에는 범프(bump)가 형성된다. 첨가제의 상호 작 용을 기반으로 하는 채움 메커니즘은 TSV 도금 공정에도 유용하게 사용된다. 다마신 공정의 미세 배선에 비하여 TSV는 100 배 이상의 크기를 가지므로 TSV 위치에 따른 첨가제의 흡착을 정확하게 파악 하는 것이 요구되며, 긴 채움 시간 동안 각 첨가제의 역할에 대해 깊이 있는 고찰을 바탕으로 채움 메커니즘을 규명하여야 한다.

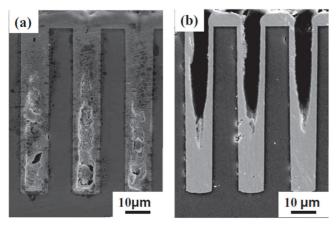

## 2-2. 구리 전해 도금을 이용한 무결함 TSV 채움

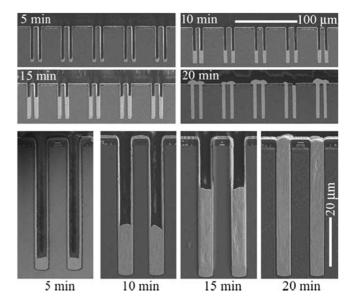

TSV 채움을 설명하기 위한 다양한 이론 중, 첨가제 흡착의 교반 의존성에 기반한 TSV 채움 메커니즘이 보고되었다. 구리 이온과 첨가제를 TSV 내부로 원활하게 공급하기 위해 교반 조건에서 TSV 채움을 진행하는데, TSV는 높은 종횡비의 구조적인 특징으로 인해 TSV 표면과 입구 근처에는 강한 강제 대류가 형성되지만 깊 이 방향으로 들어갈수록 강제 대류의 영향이 약해진다. 유체 역학 적인 시뮬레이션(simulation) 결과에 따르면, 직경 20 μm, 깊이 120 μm 의 TSV 웨이퍼를 1000 rpm에서 회전시킬 경우, TSV 바닥에서부 터 약 60% 이내의 깊이에서는 교반의 영향을 무시할 수 있다고 보 고되었다[30]. 깊이 방향에 따른 교반 세기의 변화는 첨가제의 흡착 거동 역시 TSV 위치에 따라 변할 수 있음을 시사한다. SDDACC (sulfonated diallyl dimethyl ammonium chloride copolymer)와 같은 diallylamine 계열의 유기 평탄제는 흡착 세기가 교반 세기에 비례 하는 특징을 갖는다[31-33]. Fig. 4는 SDDACC를 SPS, PEG와 함께 첨가하여 교반 조건에서 진행한 TSV 채움 결과를 나타낸다[32]. TSV 입구에서 하단부로 감에 따라 교반 세기가 점진적으로 약해지 면서 이에 비례하여 SDDACC의 흡착 세기, 즉 구리 전착의 억제 세기가 감소한다. 구리 전착 속도가 국부적으로 결정되며, 그 결과

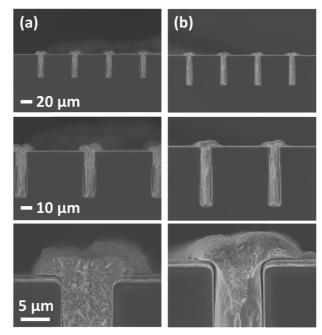

Fig. 4. Cross-section images of TSV after the Cu electrodeposition by adding (a) 0 ppm and (b) 1.5 ppm of SDDACC. Reproduced with permission from *J. Electrochem. Soc.*, 158, D715 (2011). Copyright 2011, The Electrochemical Society.

Fig. 4에 나타나 있듯이 V-shape의 형상과 함께 바닥 차오름이 진행된다. SDDACC 뿐만 아니라 JGB를 사용한 경우에도 상기의 교반의존적인 흡착을 바탕으로 V-shape의 단면이 확인된다[34,35].

TSV 전극 표면의 친수화 정도가 유기 첨가제의 흡착에 미치는 영향을 바탕으로 바닥 차오름을 효과적으로 설명할 수 있다. 유기 첨가제는 작용기에 따라 친수성 또는 소수성의 성질을 가지며, 구리 표면의 친수화(hydrophilic) 정도는 유기 첨가제의 흡착 거동에 영향을 미친다.  $Cu^{2+}$ 은 수용액 상에서 6개의 물 분자에 의해 8면체 구조(octahedral)로 수화되고, 황산염(sulfate)이 존재할 경우  $Cu^{2+}$ SO $_4^{2-}$ ( $H_2O)_5$ 의 형태로 음이온과 물 분자에 의해 안정화된다[36]. 구리 전해 도금을 진행하는 동안 구리 이온은 구리 금속으로 석출되고, 구리 이온 주변의 물 분자 혹은 음이온은 아래 식을 통해 방출된다[37].

$$Cu^{2+}(H_2O)_x(SO_4^{2-})_y + e^- \rightarrow Cu^+(H_2O)_z(SO_4^{2-})_n + (x-z)H_2O + (y-n)SO_4^{2-}$$

(1)

$$Cu^{+}(H_{2}O)_{z}(SO_{4}^{2-})_{n} + e^{-} \rightarrow Cu + zH_{2}O + nSO_{4}^{2-}$$

(2)

구리 환원과 동시에 방출되는 물 분자는 구리 표면에 존재하여 전극을 친수화한다. 친수성의 전극 표면은, 소수성의 탄소 화합물을 포함하는 중합체 계열 감속제의 흡착을 방해한다. 최근에는 상기 이론에 기반하여, 감속제 중 하나인 Tetronic 701 (PEG-PPG 공중합 체를 포함하는 폴리옥시 아민(polyoxy amine) 첨가제)을 단일로 첨 가하여 무결함 채움을 진행한 결과가 보고되었다[37]. Tetronic 701의 평균 분자량은 3,600으로, 일반적으로 구리 전해 도금에 사용하는 고분자 감속제와 분자량이 비슷하다. 수화된 구리 이온보다 감속제의 분자량이 20배 이상 높으므로 확산 속도가 느리고, 깊이 50 µm 이 상의 TSV 바닥에 구리 이온이 빠르게 도달한다. TSV 입구 근처에 서는 감속제가 흡착하는 반면, TSV 바닥에서는 먼저 도달한 구리 이온이 환원과 동시에 물 분자를 방출하여 전극 표면을 친수화한다. 친수성의 표면은 감속제의 흡착을 지속적으로 방해함으로써, 자가 촉매적(autocatalytic) 반응을 통해 TSV 바닥에서만 선택적으로 구 리가 전착된다. TSV의 입구와 벽면에서는 구리 전착이 완벽하게 억제되면서 Fig. 5와 같은 평탄한 형상의 성장 표면(growing surface)이 형성된다[37]. 감속제의 농도 구배와 더불어, TSV 전극과 기준 전극 사이의 전해질 저항으로 인한 저항손(ohmic loss)도 Fig. 5의

Fig. 5. Cross-section images of TSV after the Cu electrodeposition by adding 10 μM of Tetronic 701. Reproduced with permission from J. Electrochem. Soc., 159, D208 (2012). Copyright 2012, The Electrochemical Society.

채움 이론을 뒷받침한다[38-40]. 도금 초기에는 iR 드롭(drop)으로 인한 전압 손실로 과전압이 감소하고, 낮은 과전압에서 감속제가 TSV 표면과 벽면에 원활하게 흡착한다. 흡착한 감속제는 도금 전류를 낮추어 iR 드롭의 영향을 최소화하고, 오히려 과전압이 증가하는 양성 피드백(positive feedback)을 야기한다. 양성 피드백 이론은 과전압 증가로 인한 TSV 바닥에서의 도금 가속을 설명한다[38-40]. TSV 위치에 따른 감속제 흡착의 쌍안정(bistable) 특성을 기반으로, 아연, 주석, 금 등의 전해 도금에도 상기 메커니즘을 적용하여 무결함 TSV 채움이 가능하다[41-43].

무결함 TSV 채움을 위해 TSV 위치에 따른 억제 세기의 변화, 보다 정확하게는 TSV 입구와 벽면에서의 강한 억제와 TSV 바닥에 서의 선택적인 약한 억제가 필요함은 자명하다. 물리기상증착법을 통 해 두께 5 nm 이하의 Ta 층을 TSV 입구에만 증착함으로써 강제적 으로 구리 전착을 억제하고, 바닥 차오름을 유도할 수 있다[44,45]. TSV를 채우는 과정 중간에 산화 전류를 인가하여, TSV 입구에서만 가속제를 선택적으로 탈착하는 연구도 보고되었다[46-48]. 가속제와 감속제가 포함된 용액에서 짧은 시간 채움을 진행하고, 이후 감속 제 또는 평탄제만 포함한 용액에서 산화 전류를 인가하여 TSV 입 구에서의 가속제 탈착과 동시에 억제 물질의 흡착을 유도한다[46]. Ta 증착 또는 산화 전류를 인가하는 방법은 무결함 채움에는 적합 하지만, 추가의 공정 스텝을 요구하므로 소자의 제작 속도를 지연 하는 문제가 있다. 최근에는 첨가제를 개발하여 TSV 내에서의 전 착 속도를 국부적으로 조작하고, 추가 공정의 도입 없이 일정한 전 류를 인가하여 TSV를 채우는 연구가 보고되었다. 가속제, 감속제, 그리고 평탄제로 구성된 3-첨가제 시스템은 TSV 입구에서의 강한 억제 세기를 바탕으로 높은 종횡비의 TSV 채움에 유리하고, 또한 펄스(pulse) 전류가 아닌 정전류 도금을 통해 TSV 채움이 가능하므 로 산업에서의 니즈(needs)도 만족한다. 이후 설명할 3-첨가제 시스 템에서의 채움 메커니즘은, 상기 언급한 SDDACC 등을 포함하는 연구에 비해 첨가제 사이의 경쟁 또는 협력 효과에 대한 심화 논의

를 바탕으로 차별화하여 설명된다. 2-3장에서는 TSV 채움을 위한 3-첨가제 시스템의 개발과, 채움 메커니즘을 설명하기 위한 전기화학 분석 결과의 해석 방법에 대해 소개한다.

## 2-3. 3-첨가제 시스템에서의 채움 메커니즘

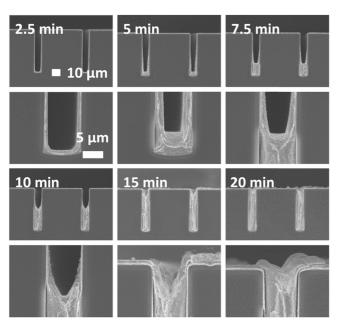

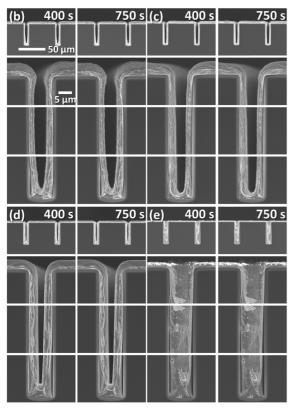

소자의 고직접화로 인해 TSV의 직경이 감소함에 따라, 고종횡비의 TSV를 채우기 위한 새로운 조합의 첨가제가 요구된다. 평탄제는 감속제와 함께 추가적인 억제 효과를 제공하여, 기존의 가속제, 감 속제의 2가지 첨가제와 함께 사용할 경우 고종횡비의 TSV 채움에 유리할 것으로 판단된다. 또한 2-2장에서 논의하였듯이 교반 세기 에 따라 흡착 세기가 변하는 평탄제를 사용하여, TSV 깊이 방향으 로의 위치에 따라 국부적으로 구리 전착 속도를 조절할 수 있다. 따 라서 가속제, 감속제, 그리고 평탄제를 포함하는 3-첨가제 시스템에서, 특히 평탄제 개발을 통해 TSV 채움을 진행하는 연구가 활발하게 진행되고 있다. 삼차 아민 또는 사차 암모늄염을 포함하는 기존의 평탄제 구조를 바탕으로, 피리딘(pyridine)을 기본 구조로 하고 말 단에 수산기(hydroxyl, -OH)를 포함하는 평탄제가 새롭게 제안되 었다[49]. SPS, PEG-PPG와 함께 피리딘 기반의 평탄제를 첨가한 3-첨가제 시스템에서 폭 9  $\mu$ m, 깊이 50  $\mu$ m의 트렌치를 결함 없이 채울 수 있으며, 900 rpm의 교반 조건에서 10 mA/cm<sup>2</sup>의 정전류를 인가 하여 채운 결과가 Fig. 6에 나타나 있다[49]. 채움이 완료될 때까지 TSV의 표면과 입구에서는 구리 전착이 완벽하게 억제되고, TSV 바닥에서만 선택적으로 구리 전착이 진행됨을 알 수 있다. 앞서 CEAC 모델에서 설명하였듯이, 바닥 차오름이 진행됨에 따라 바닥 에서의 면적 감소로 인해 SPS가 축적된다. 5~10분의 채움 시간 동 안, 특히 오목한 모서리(concave corner) 부분에서의 SPS 축적으로 인해 점차 곡면의 성장 계면(growing interface)을 형성한다.

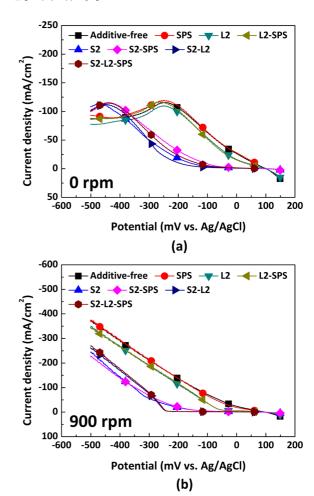

전기화학 분석은 첨가제의 거동을 확인할 수 있는 효과적인 분석 법으로, 선형주사전위법(linear sweep voltammetry, LSV), 대시간

Fig. 6. Deposition profiles after the Cu electrodeposition by adding SPS, suppressor and pyridine-based leveler containing hydroxyl group, according to the deposition time. Reproduced with permission from *J. Electrochem. Soc.*, 162, D109 (2015). Copyright 2014, The Electrochemical Society.

Fig. 7. Voltammogram with variously combined additives of SPS, suppressor (S2) and pyridine-based leveler containing hydroxyl group (L2) under the rotating speed of (a) 0 rpm, and (b) 900 rpm. Reproduced with permission from *J. Electrochem. Soc.*, 162, D109 (2015). Copyright 2014, The Electrochemical Society.

전위차법(chronopotentiometry) 등의 분석법을 사용하여 첨가제의 전기화학적인 영향을 확인하고 채움 메커니즘을 규명한다[50-53]. Fig. 6에 사용한 가속제(SPS), 감속제(PEG-PPG, S2), 그리고 피리 딘 기반의 평탄제(L2)의 영향을 확인하기 위해, 교반 세기와 첨가 제 조합에 따른 전기화학 분석이 Fig. 7과 같이 진행되었다. 900 rpm의 교반 조건에서 채움이 진행되었고, 0 rpm은 교반 세기를 무시할 수 있는 트렌치 바닥에서의 대류를, 900 rpm은 트렌치 입구 근처의 교 반 세기를 모사한 조건이다. L2의 흡착 세기는 교반 의존성을 보이며, 교반 세기가 약한 0 rpm에 비해 900 rpm의 TSV 입구 조건에서 구 리 전착을 강하게 억제하였다. 특히 L2와 S2를 함께 첨가할 경우 각각을 따로 첨가하는 것 보다 강한 억제 세기를 보이고, 강한 대류 조건의 TSV 입구 표면에서 구리 전착을 효과적으로 억제한다. 0 rpm에서 SPS와 S2를 함께 첨가하면, CEAC 모델에서 살펴봤듯이 가속제가 감속제를 치환 흡착하며 가속 효과를 보인다. 이를 종합 하여, TSV 입구에는 감속제와 평탄제가 공동 작용하여 구리 전착을 강하게 억제하고, TSV 바닥으로 갈수록 약한 교반 세기에 비례하여 평탄제의 억제 세기가 감소함을 예측할 수 있다. 전기화학 분석 결 과에는 나타나 있지 않지만, 분자량이 높은 중합체 계열의 감속제는

Fig. 8. Potential-time curve measured during the galvanostatic filling in the three-additive system composed of SPS, suppressor and pyridine-based leveler both containing amine groups. Reproduced with permission from *J. Electrochem. Soc.*, 160, D3221 (2013). Copyright 2013, The Electrochemical Society.

낮은 확산 계수로 인해 TSV 바닥에서의 농도가 낮다[54]. 따라서 TSV 바닥에서는 감속제와 평탄제의 낮은 표면 덮임률과 함께 가속 제가 지배적으로 흡착하여 바닥 차오름을 유도한다.

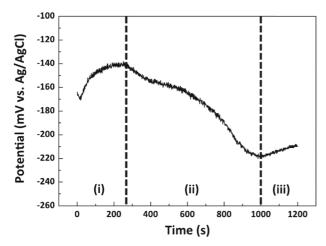

TSV 채움 동안 전압을 측정하여 채움 시간에 따른 첨가제의 상호 작용을 확인할 수 있다. 억제제의 흡착으로 인해 구리 전착이 억제 되면, 전해 도금 동안 제공되는 전자가 구리 환원에 소모되지 못하고 전극 표면에 축적된다. 이로 인해 구리 전극이 분극화(polarization) 되고 전압이 음의 방향으로 증가한다. 반대로 첨가제의 억제 효과 가 감소할 경우 탈분극화(depolarization)가 진행되어 전압이 양의 방향으로 증가한다. 말단에 아민(amine, -NH,) 작용기를 포함하는 중 합체 계열 감속제와, -NH, 말단 작용기의 피리딘 기반 평탄제를 합 성하고, 이를 포함하는 3-첨가제 시스템에서 6.5 mA/cm<sup>2</sup>의 전류 밀도를 인가하여 폭 8 μm, 깊이 40 μm의 배선을 채우는 동안 측정 한 전압 프로파일(profile)이 Fig. 8에 나타나 있다[55]. 채움 초기의 구간 (i)에서는 탈분극화로 인해 전압이 양의 값으로 이동하는데, 이는 트렌치의 바닥에서 가속제가 감속제를 치환 흡착하며 구리 전착을 가속하기 때문이다. 이후 구간 (ii)에서는 바닥 차오름이 진행됨에 따라 감속제와 평탄제의 억제 세기가 증가하여 전극이 분극화된다. 트렌치 채움이 완료된 이후의 구간 (iii)에서는, 배선을 다 채우고 과전착된 구리가 범프(bump)를 형성하며 전극 면적이 증가하고, 이로 인해 전압이 다시 양의 방향으로 이동한다.

선형주사전위법과 대시간 전위차법을 사용하여 각 첨가제의 영향과 첨가제 사이의 상호 작용을 확인할 수 있다. 나아가 채움 결과와 비교하여 TSV 깊이 방향에 따른 첨가제의 거동을 해석하고 채움 메커니즘을 규명한다. 3-첨가제 시스템은 TSV 입구에서의 강한억제와 TSV 바닥에서의 가속제 활성화를 바탕으로 바닥 차오름을유도하며, 높은 중황비의 TSV 채움에 효과적일 것으로 기대된다. 또한 첨가제 조합을 통해 TSV 채움 특성을 개선할 수 있으므로, 다양한 종류의 평탄제를 합성하여 그 영향을 규명하는 작업이 필요하다[56]. 평탄제의 작용기와 구조식에 따른 영향을 비교하고, 인가하는전압 혹은 전류의 파형을 수정하여 추가적으로 채움 성능을 개선하는연구가 진행되고 있다.

# 3. 첨가제 개발과 도금 방법 수정을 통한 TSV 채움 특성 향상

## 3-1. 첨가제 개발을 통한 채움 특성 향상

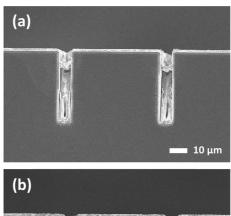

유기 첨가제의 작용기는 첨가제 자체의 흡착 거동뿐만 아니라 함께 첨가한 다른 첨가제의 흡착에도 영향을 미치면서 최종적으로 구리 전착물의 특성을 결정한다. 한 예로 말단 작용기로 술폰산염 (sulfonate)을 포함하는 첨가제를 구리 표면에 흡착시켜 구리 표면 을 친수화하면, PEG의 표면 흡착이 억제된다[25]. 반대로 메틸 (methyl) 작용기의 첨가제를 흡착시켜 표면을 소수화하면 PEG의 흡착과 억제 세기가 증가하고, 표면의 친수 혹은 소수화에 따라 중 합체 계열 첨가제의 흡착 거동이 달라짐을 확인할 수 있다[25]. 작 용기가 채움 특성에 미치는 영향을 비교하기 위해, -NH, 또는 -OH의 작용기를 포함하는 첨가제를 합성하여 배선 채움에 적용한 결과가 Fig. 9에 나타나 있다[49,55]. 각각 -NH<sub>2</sub> 그룹을 말단 작용기로 포 함하는 고분자 감속제와 피리딘(pyridine) 기반의 평탄제를 합성하 여 SPS와 함께 첨가한 경우, 트렌치의 입구로 갈수록 거친 단면의 구리 전착물이 확인되었다(Fig. 9a)[55]. 바닥 차오름이 진행되어 성장 계면이 트렌치의 입구에 가까워짐에 따라 감속제와 평탄제가 지배적으로 구리 전착물의 특성을 결정하게 된다. -NH,를 포함하는 합성 첨가제 조합은 거친 단면의 구리 전착을 야기하였고, 이는 전 착물 내부에 미세한 보이드를 포함할 수 있음을 의미한다. 이와 같은 전착물의 특성은 첨가제의 말단 작용기를 바꾸어서 개선할 수 있다. -NH, 대신 -OH 그룹을 작용기로 포함하는 감속제와 피리딘 기반의 평탄제를 합성하여 사용한 경우, Fig. 9b에 나타나 있듯이 TSV 입 구 근처에서 조밀하고 깨끗한 단면의 구리 전착이 확인되었다[49].

Fig. 9. Deposition profiles after the Cu electrodeposition by adding (a) SPS, suppressor and pyridine-based leveler both containing amine groups. Reproduced with permission from *J. Electrochem. Soc.*, 160, D3221 (2013). Copyright 2013, The Electrochemical Society. (b) SPS, suppressor and pyridine-based leveler both containing hydroxyl groups. Reproduced with permission from *J. Electrochem. Soc.*, 162, D109 (2015). Copyright 2014, The Electrochemical Society.

-OH 그룹을 포함하는 첨가제 조합은 -NH $_2$  그룹의 조합에 비해 균일한 구리 전착을 가능하게 하였고, 이는 작용기가 구리 전착물과 TSV 채움 특성을 결정한다는 것을 의미한다[49]. 다양한 작용기의 첨가제를 합성하여, 첨가제가 구리 전착에 미치는 영향을 규명하면 우수한 성능의 TSV 채움을 위한 첨가제의 개발 방향을 확립할 수 있을 것으로 기대된다.

4차 암모늄염의 양이온을 포함하는 평탄제는 할라이드(halide) 계열의 반대 이온을 통해 전기적인 중성을 유지한다. 평탄제의 유기 구조뿐 아니라 할라이드 이온도 구리 표면에 흡착하여 구리 전착 또는 다른 첨가제의 흡착에 영향을 미친다. 할라이드 이온 중 염화 이온은 구리 표면에 흡착하여 구리 이온과 구리 표면의 거리를 줄여주는 가교 역할을 한다[57]. 염화 이온의 흡착층은 구리 환원 중속도결정단계인 Cu²+ → Cu⁺ 반응의 전하전달 속도를 촉진하여 구리 환원 속도를 가속한다[58,59]. 유기 첨가제를 염화 이온과 함께 첨가할 경우, 염화 이온의 흡착층은 SPS, PEG, 싸이오 요소(thiourea) 등의 다양한 첨가제와 복합제를 형성하여 해당 첨가제의 흡착을 돕는다[60-62]. 브롬화 이온과 요오드화 이온에 대한 연구는 상대적으로 부족하지만, diallylmethylamine 계열의 공중합체와 함께 첨가한 브롬화 이온은 염화 이온에 비해 강한 교반 조건에서 억제 세기가

(a)

$$OH - X$$

$$X - N + OH$$

Leveler-X (X = I, Br or Cl)

Fig. 10. (a) Molecular structure of TEG-based levelers, Leveler-X. Deposition profiles after the Cu electrodeposition by adding (b) no leveler, (c) Leveler-Cl, (d) Leveler-Br, and (e) Leveler-I. Reproduced with permission from *J. Electrochem. Soc.*, 163, D185 (2016). Copyright 2016, The Electrochemical Society.

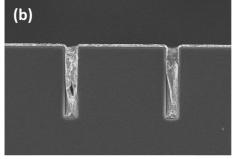

강하며, TSV 채움에도 적용 가능함이 보고되었다[63]. Fig. 10에 나타나 있듯이, 4차 암모늄염을 포함하는 triethylene glycol 기반의 평탄제에서 반대 이온의 종류만 다르게 하여, 각 첨가제가 폭 9 μm, 깊이 40 μm의 배선 채움에 미치는 영향이 확인되었다[64]. 전기화학 분석을 통해, 1000 rpm의 교반 조건에서 억제 세기가 평탄제-Cl < 평탄제-Br < 평탄제-I 순임을 확인하였다. 억제 세기가 약한 평탄제-Cl과 평탄제-Br은 배선 입구에서의 구리 전착을 허락하여 무결함 채움에 실패하였으나, 평탄제-I는 강한 억제 세기를 기반으로 바닥 차오름 채움을 가능하게 하였다.

상기 할라이드 이온에 대한 연구 결과로부터, 최근에는 요오드화 나트륨(Nal)의 무기 화합물을 평탄제로 첨가하여 TSV 크기의 트렌치 채움을 진행한 결과가 보고되었다[65]. 요오드화 이온은 가속제인 SPS의 흡착을 방해하는 한편, 감속제인 PEG-PPG의 흡착을 도와 억제 세기를 촉진한다. 요오드화 이온은 기존의 유기 평탄제와 유사하게 교반 세기에 의존하는 흡착 거동을 보이며, Fig. 11에 나타나 있듯이 폭 4, 7, 9 μm, 그리고 깊이 40 μm인 다양한 크기의 트렌치에서 바닥 차오름을 가능하게 한다[65]. 높은 전압을 인가하거나(Fig. 11b), 요오드화 이온 없이 가속제와 감속제의 2-첨가제 시스템에서 도금을 진행하는 경우(Fig. 11c), 억제 세기가 충분하지 않아 구리 전착이 벽면 혹은 입구에서 진행되어 바닥 차오름이 실패하는 것을 알 수 있다. 요오드화 이온을 포함하는 간단한 구조의무기 화합물은 단가가 저렴하므로, 유기 합성을 통해 생산되는 고가의 유기 화합물에 비해 높은 가격 경쟁력을 갖는다. 또한 일반적

Fig. 11. Deposition profiles with the addition of SPS, PEG-PPG, and NaI by applying (a) -200 mV, (b) -250 mV. (c) Filling results by adding SPS and PEG-PPG without NaI. Reproduced with permission from *J. Electrochem. Soc.*, 163, D434 (2016). Copyright 2016, The Electrochemical Society.

Korean Chem. Eng. Res., Vol. 54, No. 6, December, 2016

으로 유기 첨가제는 전해 도금 동안 분해되어 분해 산물이 생산되는데, 분해 산물이 도금 성능에 영향을 미칠 수 있으므로 도금액의 지속적인 관리가 필요하다[66,67]. 이에 반해 요오드화 이온과 같이 원소 수준의 첨가제는 분해 산물의 생성 가능성이 낮아 도금액 관리에 유리할 것으로 판단된다.

## 3-2. 도금 방법 수정을 통한 채움 특성 향상

첨가제의 개발과 더불어, 도금 변수를 수정하여 TSV 채움 특성을 개선하고 채움 시간을 줄이기 위한 연구가 지속적으로 진행되고 있 다. 인가 전압 혹은 전류에 파형을 도입함으로써 전착물의 물성을 향상시킬 수 있다. 펄스 전해 도금은 전압 혹은 전류를 인가하여 구 리 전착을 진행하는 온타임(on-time)과 구리 전착이 진행되지 않는 오프타임(off-time)으로 구성된 도금 방법이다[68]. 온타임 동안 전 착된 구리는 높은 스트레스를 보유한 상태이므로, 오프타임 동안 스트레스가 해소되며 쌍결정립계(twin boundary)를 형성한다고 알 려져 있다[69]. 쌍결정립계를 통해 전위(dislocation)의 이동은 제한 되지만 전자의 이동은 크게 방해 받지 않으므로, 쌍결정립계를 가 지는 구리 박막은 일반적인 결정립계(grain boundary)의 구리 박막 에 비해 비슷한 비저항에서 더 높은 기계적인 강도와 열적 스트레 스(thermal stress)에 대한 저항성을 갖는다[69-71]. 따라서 펄스 전 해 도금을 이용하여 TSV 내부에 쌍결정립계의 구리 전착을 진행하여 어닐링 동안의 압출(extrusion) 문제를 해결할 수 있다[70,71]. 펄스 -리벌스(pulse-reverse) 도금은 온타임과 오프타임으로 구성된 파형 중간에 산화 반응을 진행하기 위한 리벌스 스텝을 도입한 도금 방 법이다. 펄스-리벌스 도금은 TSV 입구와 벽면에 전착된 구리를 리 벌스 스텝동안 용해할 수 있어서, 고종횡비의 TSV 채움에 유리하 다[72,73]. 또한, 파형을 최적화하여 구리 전착물의 특성을 개선할 수 있는데, 리벌스 스텝 동안 표면 에너지가 높은 구리를 선택적으로 용해하여 펄스 전해 도금 대비 약 9% 낮은 비저항의 구리 박막을 전착할 수 있다[74]. 펄스-리벌스 도금법이 첨가제의 흡착과 구리 전착물의 특성에 미치는 영향이 다수 보고되었고[75-77], 이에 대 한 연구를 TSV 채움에 적용하여 특성을 개선할 수 있을 것으로 판 단된다.

펄스- 혹은 펄스-리벌스 도금 방법은 오프타임과 리벌스 스텝의 인가기가 있어 도금 시간을 줄이는데 한계가 있다. 스텝 전류 도금 법은 초기에 낮은 전류를 인가하여 일정 높이 이상 바닥 차오름을 진행한 후, 높은 전류를 인가하여 채움을 마무리하는 도금법으로 채움 시간을 효과적으로 단축할 수 있다[78]. 초기에는 보이드가 형 성되지 않는 낮은 전류를 인가하여, 바닥 차오름을 통해 성장 경계를 일정 높이 이상 형성한다. TSV의 입구에 도달할수록 감속제와 평 탄제의 표면 농도가 증가하므로, TSV 상단부에서는 높은 전류를 인가하여도 벽면에서의 구리 전착이 억제된다. 따라서 억제 세기가 강한 TSV의 상단부에서는 높은 전류를 인가하여 결함 없이 공정을 마무리하고 채움 시간을 단축한다. 15 mA의 전류를 100초, 150초, 혹은 200초 인가하고, 이후 50 mA의 높은 전류를 인가하여 폭 6.5 µm, 깊이 40 μm의 트렌치 채움 시간을 단축한 결과가 Fig. 12에 나타나 있다[79]. Figs. 12a와 b에 나타나 있듯이 바닥 차오름을 충분히 진 행하지 못하고 50 mA의 스텝 전류를 인가하는 경우, 성장 경계 근 처 벽면에서의 억제 세기가 약하여 구리 전착이 벽면에서 진행되고 결함이 발생한다[79]. 바닥 차오름을 충분히 진행한 이후 높은 스텝 전류를 인가하면, Fig. 12c에서와 같이 무결함 채움이 가능하며 정

Fig. 12. Deposition profiles with the addition of SPS, PEG-PPG, and synthesized leveler by applying (a) 15 mA (100 s)  $\rightarrow$  50 mA (150 s), (b) 15 mA (150 s)  $\rightarrow$  50 mA (135 s), and (c) 15 mA (200 s)  $\rightarrow$  50 mA (120 s). Reproduced with permission from *ECS Electrochem. Lett.*, 4, D31 (2015). Copyright 2015, The Electrochemical Society.

전류 도금 대비 채움 시간이 47% 단축된다[79]. 첨가제 개발과 더불어, 우수한 채움 특성을 유지하면서 도금 시간을 단축할 수 있는 도금법 개발에 관한 연구가 계속 진행되어야 한다.

#### 4. 결 론

본 총설에서는 차세대 3차원 소자 적층을 위한 핵심 기술 중 하나인 TSV 채움 공정에 대해 소개하였다. TSV 내부는 구리 전해 도금을 통해 채울 수 있으며, 소자의 신뢰성을 확보하기 위해 무결함 채움이 필수적이다. TSV 입구와 벽면에서는 구리 전착을 억제하고, TSV 바닥에서만 선택적으로 구리 전착을 유도하는 바닥 차오름을 통해 무결함 채움을 구현할 수 있다. 유기 첨가제는 TSV 위치에 따른 구리 전착 속도를 국부적으로 조절하여 바닥 차오름을 가능하게 한다. 가속제, 감속제, 평탄제로 구성된 3-첨가제 시스템은 고종횡비의 TSV 채움에 유리하며, 특히 평탄제의 개발을 통해 우수한 특성의 TSV 채움을 진행할 수 있을 것으로 기대된다. 전기화학 분석을 기반으로 첨가제의 거동을 이해하고 TSV 채움 메커니즘을 규명할 수 있으며, 이를 바탕으로 첨가제의 개발 방향을 확립할 것이 요구된

다. 나아가 첨가제의 작용기를 수정하여 전착물 특성을 개선하거나 도금 방법을 개발하는 연구를 통해 TSV의 채움 효율을 증진할 수 있을 것으로 판단된다.

#### References

- 1. Ryan, J. G., Geffken, R. M., Poulin, N. R. and Paraszczak, J. R., "The Evolution of Interconnection Technology at IBM," *IBM J. Res. Dev.*, **39**, 371-381(1995).

- Interconnect, ITRS (International Technology Roadmap for Semiconductors, on-line document), 2015 edition, International Technology Roadmap for Semiconductors(2015).

- Yoshinaga, T. and Nomura, M., "Trends in R&D in TSV Technology for 3D LSI Packaging," Sci. Technol. Trends, 37, 26-39 (2010).

- Lee, C. H., Hwang, S., Kim, S.-C. and Kim, J. J., "Cu Electroless Deposition onto Ta Substrates Application to Create a Seed Layer for Cu Electrodeposition," *Electrochem. Solid-State Lett.*, 9, C157-C160(2006).

- Inoue, F., Shimizu, T., Yokoyama, T., Miyake, H., Kondo, K., Saito, T., Hayashi, T., Tanaka, S., Terui, T. and Shingubara, S., "Formation of Electroless Barrier and Seed Layers in a High Aspect Ratio Through-Si Vias Using Au Nanoparticle Catalyst for All-Wet Cu Filling Technology," *Electrochim. Acta*, 56, 6245-6250(2011).

- Lim, T., Koo, H.-C., Kim, K. H., Park, K. J., Kim, M. J., Kwon, O. J. and Kim, J. J., "Room-Temperature Electroless Deposition of CoB Film and its Application as In Situ Capping during Buffing Process," *Electrochem. Solid-State Lett.*, 14, D95-D98(2011).

- Kim, K. H., Lim, T., Kim, M. J., Choe, S., Park, K. J., Ahn, S. H., Kwon, O. J. and Kim, J. J., "Direct Cu Electrodeposition on Electroless Deposited NiWP Barrier Layer on SiO2 Substrate for All-Wet Metallization Process," *J. Electrochem. Soc.*, 161, D756-D760(2014).

- 8. Park, K. J., Kim, M. J., Lim, T., Koo, H.-C. and Kim, J. J., "Conformal Cu Seed Layer Formation by Electroless Deposition in Non-Bosch through Silicon Vias," *Electrochem. Solid-State Lett.*, **15**, D26-D28(2012).

- Bernasconi, R., Molazemhosseini, A., Cervati, M., Armini, S. and Magagnin, L., "Application of Self-Assembled Monolayers to the Electroless Metallization of High Aspect Ratio Vias for Microelectronics," J. Electron. Mater., 1-7(2016).

- Kim, M. J. and Kim, J. J., "Electrodeposition for the Fabrication of Copper Interconnection in Semiconductor Devices," *Korean Chem. Eng. Res.*, 52(1), 26-39(2014).

- Cho, S. K., Kim, M. J. and Kim, J. J., "MSA as a Supporting Electrolyte in Copper Electroplating for Filling of Damascene Trenches and Through Silicon Vias," *Electrochem. Solid-State Lett.*, 14, D52-D56(2011).

- Zhu, Y., Ma, S., Sun, X., Chen, J., Miao, M. and Jin, Y., "Numerical Modeling and Experimental Verification of Through Silicon Via (TSV) Filling in Presence of Additives," *Microelectron. Eng.*, 117, 8-12(2014).

- Kong, L., Lloyd, J., Yeap, K., Zschech, E., Rudack, A., Liehr, M. and Diebold, A., "Applying X-ray Microscopy and Finite Element Modeling to Identify the Mechanism of Stress-Assisted Void

- Growth in Through-Silicon Vias, J. Appl. Phys., 110, 053502(2011).

- Nguyen, A., Fealey, K., Reilly, P., Pattanaik, G., Gracias, A., Wafula, F., Flynn, M. and Enloe, J., "Impact of Bath Stability on Electroplated Cu for TSVs in a Controlled Environment," J. Microelectron. Electron. Pack., 12, 43-48(2015).

- Kim, S.-K. and Kim, J. J., "Superfilling Evolution in Cu Electrodeposition: Dependence on the Aging Time of the Accelerator," *Electrochem. Solid-State Lett.*, 7, C98-C100(2004).

- Cho, S. K., Kim, S.-K. and Kim, J. J., "Superconformal Cu Electrodeposition Using DPS; A Substitutive Accelerator for Bis(3-sulfopropyl) Disulfide;" J. Electrochem. Soc., 152, C330-C333(2005).

- Choe, S., Kim, M. J., Kim, H. C., Cho, S. K., Ahn, S. H., Kim, S.-K. and Kim, J. J., "Degradation of Bis(3-sulfopropyl) Disulfide and Its Influence on Copper Electrodeposition for Feature Filling," *J. Electrochem. Soc.*, 160, D3179-D3185(2013).

- Kim, J. J., Kim, S.-K. and Kim, Y. S., "Catalytic Behavior of 3-Mercapto-1-propane Sulfonic Acid on Cu Electrodeposition and Its Effect on Cu Film Properties for CMOS Device Metallization," J. Electroanal. Chem., 542, 61-66(2003).

- Cho, S. K., Kim, H. C., Kim, M. J. and Kim, J. J., "Voltammetric Observation of Transient Catalytic Behavior of SPS in Copper Electrodeposition-Its Interaction with Cuprous Ion from Comproportionation," *J. Electrochem. Soc.*, 163, D428-D433(2016).

- [20] Gallaway, J. W. and West, A. C., "PEG, PPG, and Their Triblock Copolymers as Suppressors in Copper Electroplating," *J. Electrochem. Soc.*, 155, D632-D639(2008).

- Gallaway, J. W., Willey, M. J. and West, A. C., "Acceleration Kinetics of PEG, PPG, and a Triblock Copolymer by SPS During Copper Electroplating," J. Electrochem. Soc., 156, D146-D154(2009).

- 22. Gallaway, J. W., Willey, M. J. and West, A. C., "Copper Filling of 100 nm Trenches Using PEG, PPG, and a Triblock Copolymer as Plating Suppressors," *J. Electrochem. Soc.*, **156**, D287-D295(2009).

- 23. Cao, Y., Taephaisitphongse, P., Chalupa, R. and West, A. C., "Three-Additive Model of Superfilling of Copper," *J. Electrochem. Soc.*, **148**, C466-C472(2001).

- 24. Kim, S.-K., Josell, D. and Moffat, T., "Electrodeposition of Cu in the PEI-PEG-Cl-SPS Additive System: Reduction of Overfill Bump Formation During Superfilling," *J. Electrochem. Soc.*, **153**, C616-C622(2006).

- Moffat, T. P., Wheeler, D., Edelstein, M. D. and Josell, D., "Superconformal Film Growth: Mechanism and Quantification," *IBM J. Res. Dev.*, 49, 19-36(2005).

- Moffat, T., Wheeler, D., Kim, S.-K. and Josell, D., "Curvature Enhanced Adsorbate Coverage Model for Electrodeposition," *J. Electrochem. Soc.*, 153, C127-C132(2006).

- 27. Moffat, T. P. and Josell, D., "Superconformal Electrodeposition for 3-Dimensional Interconnects," *Isr. J. Chem.*, **50**, 312-320(2010).

- 28. Cho, S.-K., Kim, M.-J., Koo, H.-C., Kim, S.-K. and Kim, J.-J., "An Empirical Relation Between the Plating Process and Accelerator Coverage in Cu Superfilling," *Bull. Korean Chem. Soc.*, **33**, 1603-1607(2012).

- 29. Moffat, T., Bonevich, J., Huber, W., Stanishevsky, A., Kelly, D., Stafford, G. and Josell, D., "Superconformal Electrodeposition of Copper in 500-90 nm Features," *J. Electrochem. Soc.*, **147**, 4524-4535(2000).

- 30. Zhang, Y., Ding, G., Wang, H. and Cheng, P., "Effect of External Factors on Copper Filling in 3D Integrated Through-Silicon-

732 김회철 · 김재정

- Vias (TSVs)," J. Electrochem. Soc., 162, D427-D434(2015).

- 31. Kondo, K., Suzuki, Y., Saito, T., Okamoto, N. and Takauchi, M., "High Speed Through Silicon Via Filling by Copper Electrode-position," *Electrochem. Solid-State Lett.*, **13**, D26-D28(2010).

- Hayashi, T., Kondo, K., Saito, T., Takeuchi, M. and Okamoto, N., "High-Speed Through Silicon Via(TSV) Filling Using Diallylamine Additive II. Optimization of Diallylamine Concentration," *J. Electro-chem. Soc.*, 158, D715-D718(2011).

- Hayashi, T., Kondo, K., Saito, T., Okamoto, N., Yokoi, M., Takeuchi, M., Bunya, M., Marunaka, M. and Tsuchiya, T., "Correlation Between Filled Via and Produced Cuprous Ion Concentration by Reverse Current Waveform," *J. Electrochem. Soc.*, 160, D256-D259(2013).

- Sun, J.-J., Kondo, K., Okamura, T., Oh, S., Tomisaka, M., Yonemura, H., Hoshino, M. and Takahashi, K., "High-Aspect-Ratio Copper Via Filling Used for Three-Dimensional Chip Stacking," *J. Electrochem. Soc.*, 150, G355-G358(2003).

- Lühn, O., Van Hoof, C., Ruythooren, W. and Celis, J.-P., "Filling of Microvia with an Aspect Ratio of 5 by Copper Electrodeposition," *Electrochim. Acta*, 54, 2504-2508(2009).

- Casas, J., Alvarez, F. and Cifuentes, L., "Aqueous Speciation of Sulfuric Acid-Cupric Sulfate Solutions," *Chem. Eng. Sci.*, 55, 6223-6234(2000).

- Moffat, T. and Josell, D., "Extreme Bottom-Up Superfilling of Through-Silicon-Vias by Damascene Processing: Suppressor Disruption, Positive Feedback and Turing Patterns," J. Electrochem. Soc., 159, D208-D216(2012).

- 38. Josell, D., Wheeler, D. and Moffat, T., "Modeling Extreme Bottom-Up Filling of Through Silicon Vias," *J. Electrochem. Soc.*, **159**, D570-D576(2012).

- Wheeler, D., Moffat, T. and Josell, D., "Spatial-Temporal Modeling of Extreme Bottom-Up Filling of Through-Silicon-Vias," *J. Electrochem. Soc.*, 160, D3260-D3265(2013).

- Yang, L., Radisic, A., Deconinck, J. and Vereecken, P. M., "Stochastic Modeling of Polyethylene Glycol as a Suppressor in Copper Electroplating," J. Electrochem. Soc., 161, D269-D276(2014).

- Josell, D. and Moffat, T., "Extreme Bottom-Up Filling of Through Silicon Vias and Damascene Trenches With Gold in a Sulfite Electrolyte," J. Electrochem. Soc., 160, D3035-D3039(2013).

- 42. Josell, D. and Moffat, T., "Bottom-Up Electrodeposition of Zinc in Through Silicon Vias," *J. Electrochem. Soc.*, **162**, D129-D135(2015).

- 43. Josell, D. and Moffat, T., "Superconformal Bottom-Up Nickel Deposition in High Aspect Ratio Through Silicon Vias," *J. Electrochem. Soc.*, **163**, D322-D331(2016).

- Lühn, O., Radisic, A., Vereecken, P., Van Hoof, C., Ruythooren, W. and Celis, J.-P., "Changing Superfilling Mode for Copper Electrodeposition in Blind Holes from Differential Inhibition to Differential Acceleration," *Electrochem. Solid-State Lett.*, 12, D39-D41(2000)

- 45. Lühn, O., Radisic, A., Van Hoof, C., Ruythooren, W. and Celis, J.-P., "Monitoring the Superfilling of Blind Holes with Electrodeposited Copper," *J. Electrochem. Soc.*, **157**, D242-D247(2010).

- Hayase, M. and Otsubo, K., "Copper Deep Via Filling with Selective Accelerator Deactivation by a Reverse Pulse," *J. Electrochem. Soc.*, 157, D628-D632(2010).

- 47. Matsuoka, T., Otsubo, K., Onishi, Y., Amaya, K. and Hayase, M., "Inverse Analysis of Accelerator Distribution in Copper Through

- Silicon Via Filling," Electrochim. Acta, 82, 356-362(2012).

- Hayase, M. and Nagao, M., "Copper Deep Via Filling with Selective Accelerator Deactivation by Polyethyleneimine," *J. Electrochem.* Soc., 160, D3216-D3220(2013).

- Kim, H. C., Choe, S., Cho, J. Y., Lee, D., Jung, I., Cho, W.-S., Kim, M. J. and Kim, J. J., "Bottom-Up Filling of Through Silicon Vias Using Galvanostatic Cu Electrodeposition with the Modified Organic Additives," J. Electrochem. Soc., 162, D109-D114(2015).

- Moffat, T., Wheeler, D. and Josell, D., "Electrodeposition of Copper in the SPS-PEG-Cl Additive System I. Kinetic Measurements: Influence of SPS," *J. Electrochem. Soc.*, 151, C262-C271 (2004).

- 51. Delbos, E., Omnès, L. and Etcheberry, A., "Bottom-Up Filling Optimization for Efficient TSV Metallization," *Microelectron. Eng.*, **87**, 514-516(2010).

- 52. Tsai, T.-H. and Huang, J.-H., "Copper Electrodeposition in a Through-Silicon Via Evaluated by Rotating Disc Electrode Techniques," *J. Micromech. Microeng.*, **20**, 115023(2010).

- Cao, H., Hang, T., Ling, H. and Li, M., "Behaviors of Chloride Ions in Methanesulfonic Acid Bath for Copper Electrodeposition of Through-Silicon-Via," J. Electrochem. Soc., 160, D146-D149(2013).

- Yang, L., Radisic, A., Deconinck, J. and Vereecken, P. M., "Modeling the Bottom-Up Filling of Through-Silicon Vias Through Suppressor Adsorption/Desorption Mechanism," *J. Electrochem. Soc.*, 160, D3051-D3056(2013).

- 55. Kim, M. J., Kim, H. C., Choe, S., Cho, J. Y., Lee, D., Jung, I., Cho, W.-S. and Kim, J. J., "Cu Bottom-Up Filling for Through Silicon Vias with Growing Surface Established by the Modulation of Leveler and Suppressor," *J. Electrochem. Soc.*, 160, D3221-D3227(2013).

- 56. Kim, M. J., Seo, Y., Kim, H. C., Lee, Y., Choe, S., Kim, Y. G., Cho, S. K. and Kim, J. J., "Galvanostatic Bottom-Up Filling of TSV-like Trenches: Choline-based Leveler Containing Two Quaternary Ammoniums," *Electrochim. Acta*, 163, 174-181(2015).

- 57. Yanson, Y. I. and Rost, M. J., "Structural Accelerating Effect of Chloride on Copper Electrodeposition," *Angew. Chem. Int. Ed.*, **52**, 2454-2458(2013).

- Nagy, Z., Blaudeau, J., Hung, N., Curtiss, L. and Zurawski, D.,

"Chloride Ion Catalysis of the Copper Deposition Reaction," *J. Electrochem. Soc.*, 142, L87-L89(1995).

- Moffat, T. P. and Yang, L.-Y. O., "Accelerator Surface Phase Associated with Superconformal Cu Electrodeposition," *J. Electrochem. Soc.*, 157, D228-D241(2010).

- Feng, Z. V., Li, X. and Gewirth, A. A., "Inhibition Due to the Interaction of Polyethylene Glycol, Chloride, and Copper in Plating Baths: a Surface-Enhanced Raman Study," *J. Phys. Chem. B*, 107, 9415-9423(2003).

- Dow, W.-P., Huang, H.-S., Yen, M.-Y. and Chen, H.-H., "Roles of Chloride Ion in Microvia Filling by Copper Electrodeposition II. Studies Using EPR and Galvanostatic Measurements," J. Electrochem. Soc., 152, C77-C88(2005).

- 62. Kim, H. C., Kim, M. J., Choe, S., Lim, T., Park, K. J., Kim, K. H., Ahn, S. H., Kim, S.-K. and Kim, J. J., "Electrodeposition of Cu Films with Low Resistivity and Improved Hardness Using Additive Derivatization," *J. Electrochem. Soc.*, 161, D749-D755 (2014).

- 63. Kondo, K., Yamada, Y. and Yokoi, M., "TSV Fillings and Elec-

- trochemical Measurements of the Dialyl-amine Additive with Cl<sup>-</sup> and Br<sup>-</sup>, *J. Electrochem. Soc.*, **162**, D397-D400(2015).

- 64. Kim, M. J., Seo, Y., Oh, J. H., Lee, Y., Kim, H. C., Kim, Y. G. and Kim, J. J., "Communication-Halide Ions in TEG-Based Levelers Affecting TSV Filling Performance," J. Electrochem. Soc., 163, D185-D187(2016).

- Kim, M. J., Kim, H. C. and Kim, J. J., "The Influences of Iodide Ion on Cu Electrodeposition and TSV Filling," *J. Electrochem. Soc.*, 163, D434-D441(2016).

- 66. Choe, S., Kim, M. J., Kim, H. C., Lim, T., Park, K. J., Kim, K. H., Ahn, S. H., Lee, A., Kim, S.-K. and Kim, J. J., "Degradation of Poly(ethylene glycol-propylene glycol) Copolymer and Its Influences on Vopper Electrodeposition," *J. Electroanal. Chem.*, 714-715, 85-91(2014).

- 67. Choe, S., Kim, M. J., Kim, K. H., Kim, H. C., Jeon, Y., Kim, T. Y., Kim, S.-K. and Kim, J. J., "High Accuracy Concentration Analysis of Accelerator Components in Acidic Cu Superfilling Bath," *J. Electrochem. Soc.*, 163, D33-D39(2016).

- Kim, M. J., Cho, S. K., Koo, H.-C., Lim, T., Park, K. J. and Kim, J. J., "Pulse Electrodeposition for Improving Electrical Properties of Cu Thin Film," *J. Electrochem. Soc.*, 157, D564-D569(2010).

- Lu, L., Shen, Y., Chen, X., Qian, L. and Lu, K., "Ultrahigh Strength and High Electrical Conductivity in Copper," *Science*, 304, 422-426(2004).

- Jin, S., Wang, G. and Yoo, B., "Through-Silicon-Via (TSV) Filling by Electrodeposition of Cu with Pulse Current at Ultra-Short Duty Cycle," *J. Electrochem. Soc.*, 160, D3300-D3305(2013).

- Jin, S., Seo, S., Wang, G and Yoo, B., "Electrodeposition of Nanotwin Cu by Pulse Current for Through-Si-Via (TSV) Process," *J. Nanosci. Nanotechnol.*, 16, 5410-5414(2016).

- 72. Hong, S. C., Lee, W. G., Kim, W. J., Kim, J. H. and Jung, J. P.,

- "Reduction of Defects in TSV Filled with Cu by High-Speed 3-Step PPR for 3D Si Chip Stacking," *Microelectron. Reliab.*, **51**, 2228-2235(2011).

- Zhu, Q., Toda, A., Zhang, Y., Itoh, T. and Maeda, R., "Void-Free Copper Filling of Through Silicon Via by Periodic Pulse Reverse Electrodeposition," *J. Electrochem. Soc.*, 161, D263-D268(2014).

- 74. Kim, M. J., Lim, T., Park, K. J., Cho, S. K., Kim, S.-K. and Kim, J. J., "Characteristics of Pulse-Reverse Electrodeposited Cu Thin Films: I. Effects of the Anodic Step in the Absence of an Organic Additive," *J. Electrochem. Soc.*, 159, D538-D543(2012).

- Kim, M. J., Lim, T., Park, K. J., Kwon, O. J., Kim, S.-K. and Kim, J. J., "Characteristics of Pulse-Reverse Electrodeposited Cu Thin Film: II. Effects of Organic Additives," *J. Electrochem. Soc.*, 159, D544-D548(2012).

- Kim, M. J., Lim, T., Park, K. J., Kim, S.-K. and Kim, J. J., "Pulse-Reverse Electrodeposition of Cu for the Fabrication of Metal Interconnection I. Effects of Anodic Steps on the Competitive Adsorption of the Additives Used for Superfilling," *J. Electrochem. Soc.*, 160, D3081-D3087(2013).

- Kim, M. J., Lim, T., Park, K. J., Kim, S.-K. and Kim, J. J., "Pulse-Reverse Electrodeposition of Cu for the Fabrication of Metal Interconnection II. Enhancement of Cu Superfilling and Leveling," J. Electrochem. Soc., 160, D3088-D3092(2013).

- Wang, Z., Wang, H., Cheng, P., Ding, G. and Zhao, X., "Simultaneous Filling of Through Silicon Vias (TSVs) with Different Aspect Ratios Using Multi-Step Direct Current Density," J. Micromech. Microeng., 24, 085013(2014).

- Kim, H. C., Kim, M. J., Seo, Y., Lee, Y., Choe, S., Kim, Y. G., Cho,

S. K. and Kim, J. J., "Bottom-Up Filling of TSV-Scaled Trenches

by Using Step Current Electrodeposition," *ECS Electrochem. Lett.*, 4, D31-D34(2015).