### LETTERS Open Access

# Accurate extraction of WSe2 FETs parameters by using pulsed I-V method at various temperatures

Sung Tae Lee, In Tak Cho, Won Mook Kang, Byung Gook Park and Jong-Ho Lee\*

#### **Abstract**

This work investigates the intrinsic characteristics of multilayer WSe $_2$  field effect transistors (FETs) by analysing Pulsed *I-V* (PIV) and DC characteristics measured at various temperatures. In DC measurement, unwanted charge trapping due to the gate bias stress results in *I-V* curves different from the intrinsic characteristic. However, PIV reduces the effect of gate bias stress so that intrinsic characteristic of WSe $_2$  FETs is obtained. The parameters such as hysteresis, field effect mobility ( $\mu_{eff}$ ), subthreshold slope (SS), and threshold voltage ( $V_{th}$ ) measured by PIV are significantly different from those obtained by DC measurement. In PIV results, the hysteresis is considerably reduced compared with DC measurement, because the charge trapping effect is significantly reduced. With increasing temperature, the field effect mobility ( $\mu_{eff}$ ) and subthreshold swing (SS) are deteriorated, and threshold voltage ( $V_{th}$ ) decreases.

Keywords: Two-dimensional materials, WSe<sub>2</sub> FETs, Pulsed I-V method, DC method, Temperature

#### 1 Background

Two-dimensional(2D) layered materials such as graphene and boron nitride offer new opportunities in the field of electronics with its excellent physical, chemical properties [1–6]. Though graphene has been studied most widely, its lack of bandgap limits its application. Transition metal dichalcogenides (TMDCs) provide a solution to this problem with their sizable bandgap energy and ultra-thin form of layers. Among them, WSe<sub>2</sub> FETs can be very appealing for the nanoscale electronic applications and blackplanes for flat panel display (FPD) due to their high mobility ( $\sim 100~\rm cm^2/V \cdot s$ ), excellent on/off ratio( $\sim 10^7$ ), and low subthreshold swing (SS,  $\sim 70~\rm mV/decade$ ) [7–9].

When we simulate the circuits which consist of  $WSe_2$  FETs, it is necessary to know the parameters of the FETs. Most of the parameters reported up to now were extracted from the I-V characteristics obtained by the DC method. However, these values were not correct, because a large hysteresis is observed due to the gate bias

stress during the DC measurement [10–12]. On the other hand, in the Pulsed I-V (PIV) measurement, the effect of gate bias stress is reduced greatly so that intrinsic characteristic of WSe<sub>2</sub> FETs can be obtained [13, 14]. Thus PIV method is considered as a reasonable method for estimating the performance and reliability of semiconductor devices. The purpose of PIV method is to avoid the negative effects such as self-heating and transient trapped charges. Therefore, the PIV method can provide the accurate device parameters needed for improved computer-aided-engineering (CAE) software models. However, there have been no reports on the parameter extraction from the fabricated WSe<sub>2</sub> FETs at various temperatures. In this work, we show the *I-V* curves measured by PIV and DC measurement methods, and compare the parameters extracted from the results obtained by both methods at various temperatures (-30 to 40 °C).

#### 2 Experimental details

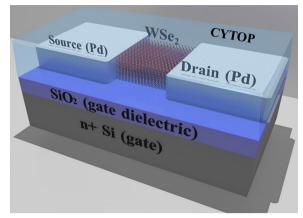

Figure 1 shows the perspective view of the structure of a multilayer WSe<sub>2</sub> FET with the bottom gate structure. An n-type silicon wafer which was heavily doped ( $\rho \sim 0.005$   $\Omega \cdot \text{cm}$ ) by phosphorus is used as a starting substrate and also plays a role as back-gate electrodes. After thermal

\*Correspondence: jhl@snu.ac.kr Department of Electrical and Computer Engineering, Seoul National University, Seoul 151-747, South Korea

**Fig. 1** Schematic diagram of multi-layer WSe<sub>2</sub> FETs with a heavily *n*-doped Si bottom-gate and Pd source/drain contact

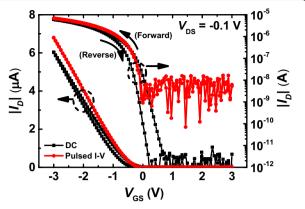

**Fig. 2** Comparison of  $I_{\rm D}$ - $V_{\rm GS}$  characteristics of a WSe $_2$  FET measured by DC method and PIV ( $t_{\rm on}=10^{-4}$  s,  $t_{\rm off}=1$  s,  $V_{\rm base}=0$  V) methods at 20 °C

oxidation in dry oxygen at 950 °C, 35 nm thick thermal oxide which serves as gate insulator was grown on the heavily doped Si wafer. Then, WSe<sub>2</sub> flakes were mechanically exfoliated from bulk WSe2 crystals and transferred on SiO<sub>2</sub>/Si substrate by using a polydimethylsiloxane (PDMS) stamp. The multi-layer WSe2 flakes on the substrate were annealed at 350 °C for 2 h in the ambient of a mixed gas of argon and hydrogen. Photolithographic patterning and electron beam evaporation of Pd (~70 nm), followed by lift-off in acetone, create source and drain electrodes on the WSe2 flakes with a good Ohmic contact. However, one of the key limitations for TMDC devices, like other types of low-dimensional material, comes from the intrinsic nature of instability associated with easy adsorption of gaseous molecules such as oxygen and moisture due to the large surface areas of lowdimensional materials. Absorbed gaseous molecules and moisture can act as a charge trap site [15]. To prevent the molecules being absorbed, we adopted flourinated polymer (CYTOP; CTL-809 M, Asahi Glass Co., Ltd) passivation so that the drift of the drain current in MoS<sub>2</sub> FETs was reduced greatly [16]. Therefore, the backside of the WSe2 flake was encapsulated by the CYTOP with typical spin coating process. Then, after thermal evaporation of SiOx(~50 nm) on the CYTOP, for a surface promoter layer during PR coating, pad opening was completed by dry etching( $\sim$ SF<sub>6</sub>/CF<sub>4</sub>) via PR patterns.

#### 3 Result and discussion

Figure 2 shows the transfer curves ( $I_{\rm D}-V_{\rm GS}$ ) measured at 20 °C from the FET with a W/L of 30/10  $\mu$ m at a drainto-source voltage ( $V_{\rm DS}$ ) of -0.1 V. We carried out the measurement using WGFMU (Waveform Generator and Fast Measurement Unit) module installed in an Agilent B1500 semiconductor parameter analyser. In DC and PIV

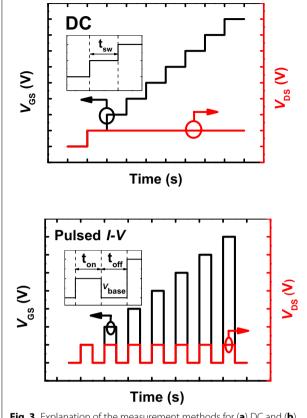

measurement, the  $V_{GS}$  is scanned from 3 to -3 V (forward) and then from -3 to 3 V (reverse). The transfer curves obtained by DC measurement show a large hysteresis. Because of the  $V_{\rm GS}$  stress during the DC measurement, the charges can be trapped or de-trapped at the WSe<sub>2</sub>/ SiO<sub>2</sub> interface and/or the backside of WSe<sub>2</sub> flakes, therefore the threshold voltage  $(V_{th})$  can be shifted positively or negatively. In Fig. 2, we can clearly observe the hysteresis in DC  $I_D$ – $V_{GS}$  curves represented by square symbols, but not in the PIV curves. The drain currents measured by the DC method are smaller than those measured by the PIV method when the  $V_{\rm GS}$  is larger than  $V_{\rm th}$  in magnitude. If we extract the carrier mobility from the DC  $I_D$ - $V_{GS}$ curves, the mobility seems to be degraded. Since some of the trapped charges stay trapped until the gate polarity is switched in the DC measurement, the large hysteresis is observed in DC measurement [17]. Note the off-current obtained by the PIV method is much higher than that obtained by the DC method in Fig. 2 because the low limit of the WGFMU module in measurement current is  $\sim 10^{-8}$ A. In PIV measurement, we investigated the optimized condition to reduce gate bias stress as small as possible. Figure 3a, b depict bias scheme for the DC and Pulsed I-V measurements, respectively. The  $t_{\rm sw}$  in the inset of Fig. 3a represents the step width at each bias step. The drain bias  $(V_{\rm DS})$  is fixed at  $-0.1~{\rm V}$  from the start of the measurement. The  $t_{\rm on}$ ,  $t_{\rm off}$ , and  $V_{\rm base}$  in the inset of Fig. 3b stand for turn-on pulse width  $(10^{-4} \text{ s})$ , turn-off pulse width (1 s), and the bias during turn-off (0 V), respectively [17]. During the period, both rise and fall times are  $10^{-7}$ s. The  $V_{\rm GS}$ pulse during  $t_{\rm off}$  is set to 0 V to minimize the  $V_{\rm GS}$  stress effect. Shorter  $t_{on}$  and longer  $t_{off}$  are necessary to suppress the effect of the trapping and detrapping of the charges. Note the drain bias is synchronized with the gate bias and the bias is -0.1 V during  $t_{on}$ .

**Fig. 3** Explanation of the measurement methods for (**a**) DC and (**b**) PIV methods. The insert in **a** explains the step width at each bias step  $(t_{sw})$ . The  $t_{onv}$   $t_{offv}$  and  $V_{base}$  in the inset of **b** are  $10^{-4}$  s, 1 s, and 0 V, respectively. In PIV, the drain bias is synchronized with the gate bias

Figure 4a, b show the transfer curves measured by DC and PIV methods, respectively, at various temperatures at a  $V_{\rm DS}$  of -0.1 V. As mentioned in Fig. 2, the hysteresis is much suppressed by measuring the device with the PIV method. Mobility ( $\mu_{\rm eff}$ ), subthreshold swing (SS),  $V_{\rm th}$  are extracted from the transfer curves at various temperatures.

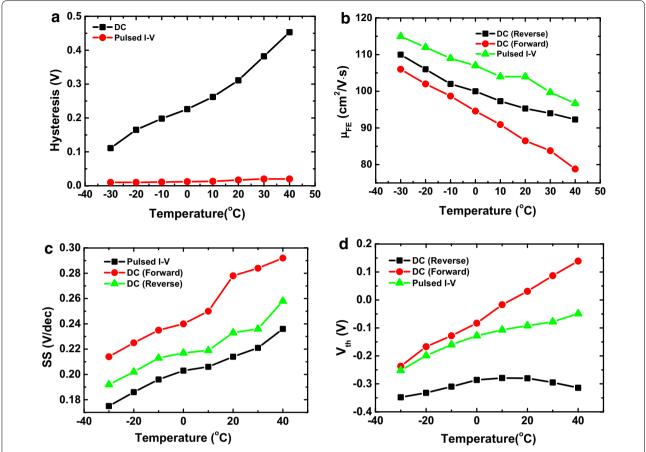

In Fig. 5, shown is temperature dependency of electrical parameters extracted from transfer curves of multilayer WSe<sub>2</sub> FETs. In Fig. 5a, the hysteresis is clearly observed in the  $I_{\rm D}$ – $V_{\rm GS}$  curves obtained by DC method, but ignorable hysteresis in the curves measured by PIV method. The hysteresis was defined as the  $V_{\rm GS}$  difference at a fixed drain current of  $10^{-8}$  A between the forward and reverse scans. Electrons or holes during the measurement of the DC method can be trapped or detrapped into the traps at the interface due to  $V_{\rm GS}$  stress, which leads to a positive or negative shift in the  $V_{\rm th}$ . As the temperature increases, the hysteresis in the curves measured by DC method increases because elevated temperature activates the trapping and detrapping process of carriers.

**Fig. 4** a Transfer curves of multilayer WSe $_2$  FET measured by DC method using the bias scheme shown in Fig. 3a at various temperatures (-30 to 40 °C). **b** Transfer curves of multilayer WSe $_2$  FET measured by PIV method using the bias scheme shown in Fig. 3b at various temperatures (-30 to 40 °C)

It seems that the time constants for the carrier trapping and detrapping in given temperature range are longer than the  $t_{\rm on}$  ( $10^{-4}$  s) used in this work so that the increase of hysteresis during PIV method can be ignorable. The variation of the hysteresis with the  $t_{\rm on}$  was studied in [17].

Figure 5b shows the temperature dependency of mobility. The field effect mobility was extracted from the maximum point of transconductance  $(g_m)$  using the following equation

$$\mu_{eff} = \frac{Lg_m}{WC_i V_{DS}} \tag{1}$$

where C and  $g_{\rm m}$  are gate capacitance per unit area and the transconductance, respectively. The  $\mu_{\rm eff}$  was deteriorated as the temperature increases from -30 to 40 °C. Phonon scattering is enhanced with rising temperature, which leads to the degradation in the carrier mobility. According to the relation of  $\mu_{\rm eff} \propto T^{-\gamma}$ , the  $\gamma$ s for the forward and reverse scans are 1.149 and 0.682, respectively. However, the decrease rate obtained by the PIV is

Fig. 5 Temperature dependency of **a** hysteresis, **b** field effect mobility, **c** subthreshold swing, **d** threshold voltage obtained from multilayer WSe<sub>2</sub> FET. All parameters are extracted from transfer curves

0.646. The mobility measured by PIV method is greater than the mobility measured by DC method, because in the DC measurement hole was trapped and it decreases the current, which decreases apparently the effective mobility. However, in Pulsed I-V measurement, the trapped hole was detrapped during  $t_{\text{off}}$  and the mobility was not degraded appreciably. Besides, mobility measured in DC forward scan is lower than the mobility measured in DC reverse scan. The hole density in the channel is reduced due to the charge (hole) trapping during DC forward scan, so the slope of I-V curves is reduced, which results in reduced mobility. During DC reverse scan, the discharging is mainly occurred by hole emission to the valance band. The holes need some energy to be emitted to the valence band. Therefore, the traps do not discharge significantly until the gate bias is below threshold voltage  $(V_{\rm th})$ , so the carrier density in the channel is reduced.

In addition, as the temperature rises, the difference between the mobility measured by DC forward and reverse scans increases as shown in Fig. 5b. The reason for the difference is explained as follows. Compared to the case of the forward scan, the holes in the reverse scan are increasingly emitted to the valence band with increasing temperature since increasing temperature increases the energy of the holes trapped.

Figure 5c shows subthreshold swing (SS) measured at various temperatures. The SS was defined as  $V_{\rm GS1}(V_{\rm GS}$  at  $I_d=10^{-9}~{\rm A})-V_{\rm GS2}(V_{\rm GS}$  at  $I_d=10^{-8}~{\rm A})$ . As temperature increases, the SS increases as given by

$$SS = 2.3 \frac{kT}{q} \left( 1 + \frac{C_{dm}}{C_{ox}} \right). \tag{2}$$

SS measured by DC measurement is greater than SS measured by PIV, because charge trapping decreases the current in DC measurement which makes SS larger. Furthermore, SS measured by DC forward scan is larger than the SS measured by DC reverse scan, because as explained above the slope of DC forward scan is smaller than that of DC reverse scan. The difference between SS measured by DC forward scan and SS measured by DC reverse scan increases as temperature rises. This

phenomenon can be explained by the physics explained in the mobility difference with the temperature.

The threshold voltage  $(V_{\rm th})$  was calculated by reading a gate-source voltage  $(V_{\rm GS})$  at a constant current  $(I_{\rm d}=10^{-8}~{\rm A})$ . In PIV method, the threshold voltage shifts to the positive direction due to the increase of thermally activated carrier density. At any temperature, the threshold voltage measured by DC forward scan is in the rightmost position, and the threshold voltage measured by DC reverse scan is in the leftmost position. The reason can be explained as follows. During DC forward scan, the electron was trapped before  $V_{\rm GS}$  reaches  $V_{\rm th}$  so the threshold voltage moves to the right. On the other hand, during DC reverse scan, the hole was trapped before  $V_{\rm GS}$  reaches  $V_{\rm th}$  so the threshold voltage moves to the left. Furthermore, the difference between  $V_{\rm th}$ s measured by DC forward and reverse scans increases with increasing temperature, since the hysteresis increases.

#### 4 Conclusions

In this paper, we extracted key parameters of WSe<sub>2</sub> FETs accurately at various temperatures by adopting pulsed I-V (PIV) method. The behavior of these parameters are different from that of the parameters obtained by DC method. For example, the decrease rates of the hole mobility are 1.149 and 0.646, respectively, for DC (forward scan) and PIV methods. By using PIV method, we could obtain accurate behavior of hysteresis, hole mobility, subthreshold swing, and threshold voltage with increasing temperature. We observed notable degradation of parameter with increasing temperature. The mobility is degraded, subthreshold swing increases and threshold voltage moves to the right as temperature rises. The parameters obtained by using PIV method are accurate and will be useful in the simulation of WSe<sub>2</sub> FETs circuit at various temperatures.

#### Authors' contributions

All authors have contributed to the writing of the manuscript. All authors read and approved the final manuscript.

#### Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF-2016R1A2B3009361) and the Brain Korea 21 Plus Project in 2016.

#### **Competing interests**

The authors declare that they have no competing interests.

Received: 9 August 2016 Accepted: 17 October 2016 Published online: 21 November 2016

#### References

- B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, Nat Nanotechnol 6. 147–150 (2011)

- 2. B. Radisavljevic, A. Kis, Nat Mater 12, 815–820 (2013)

- 3. Y. Yoon, K. Ganapathi, S. Salahuddin, Nano Lett **11**, 3768–3773 (2011)

- O. Lopez-Sanchez, D. Lembke, M. Kayci, A. Radenovic, A. Kis, Nat Nanotechnol 8, 497–501 (2013)

- F.K. Perkins, A.L. Friedman, E. Cobas, P.M. Campbell, G.G. Jernigan, B.T. Jonker, Nano Lett 13, 668–673 (2013)

- 6. D.J. Late et al., ACS Nano 7, 4879–4891 (2013)

- H. Fang, S. Chuang, T.C. Chang, K. Takei, T. Takahashi, A. Javey, Nano Lett 12, 3788–3792 (2012)

- W. Liu, J. Kang, D. Sarkar, Y. Khatami, D. Jena, K. Banerjee, Nano Lett 13, 1983–1990 (2013)

- 9. W. Liu, W. Cao, J. Kang, K. Banerjee, ECS Trans 58(7), 281–285 (2013)

- D.J. Late, B. Liu, H.R. Matte, V.P. Dravid, C.N.R. Rao, ACS Nano 6, 5635–5641 (2012)

- W. Park, Y. G. Lee, J. J. Kim, S. K. Lee, C. G. Kang, C. Cho, and B. H. Lee, in International Conference on Solid State Device and Materials, SSDM, 2013, pp. 684–685

- 12. D. Estrada, S. Dutta, A. Liao, E. Pop, Nanotechnology 21(8), 085702 (2010)

- I. Meric, C.R. Dean, A.F. Young, N. Baklitskaya, N.J. Tremblay, C. Nuckolls, K.L. Shepard, Nano Lett 11(3), 1093–1097 (2011)

- J.M. Park, D. Lee, J. Shim, T. Jeon, K. Eom, B.G. Park, J.H. Lee, Semicond Sci Technol 29(9), 095006 (2014)

- 15. Y.G. Lee et al., Appl Phys Lett 102, 093121 (2013)

- 16. Roh et al., Nanotechnology **26**, 455201 (2015)

- J.-M. Park, I. Tak, W. Kang, B. G. Park and J. H. Lee, in *International Conference on Electronics, Information, and Communication (ICEIC)*, 2016, pp. 369–372

## Submit your manuscript to a SpringerOpen journal and benefit from:

- ► Convenient online submission

- ► Rigorous peer review

- ► Immediate publication on acceptance

- ► Open access: articles freely available online

- ► High visibility within the field

- Retaining the copyright to your article

Submit your next manuscript at ▶ springeropen.com